%EB%B0%98%EB%8F%84%EC%B2%B4

-

60% 이상 챗GPT 추론 성능 향상할 NPU 핵심기술 개발

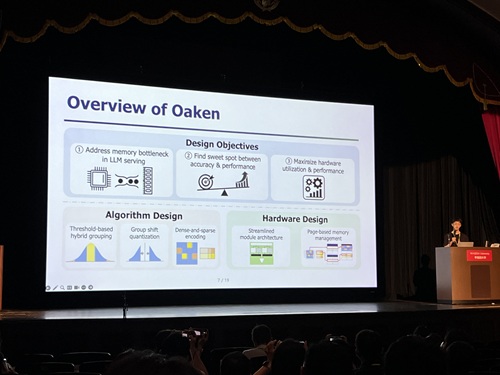

오픈AI 챗GPT4, 구글 Gemnini 2.5 등 최신 생성형AI 모델들은 높은 메모리 대역폭(Bandwidth) 뿐만 아니라 많은 메모리 용량(Capacity)를 필요로 한다. 마이크로소프트, 구글 등 생성형AI 클라우드 운영 기업들이 엔비디아 GPU를 수십만 장씩 구매하는 이유다. 이런 고성능 AI 인프라 구축의 핵심 난제를 해소할 방안으로, 한국 연구진이 최신 GPU 대비 약 44% 낮은 전력 소모에도 평균 60% 이상 생성형 AI 모델의 추론 성능을 향상할 NPU(신경망처리장치)* 핵심 기술을 개발하는데 성공했다.

*NPU(Neural Processing Unit): 인공신경망(Neural Network)을 빠르게 처리하기 위해 만든 AI 전용 반도체 칩

우리 대학 전산학부 박종세 교수 연구팀과 (주)하이퍼엑셀(전기및전자공학부 김주영 교수 창업기업)이 연구 협력을 통해, 챗GPT와 같은 생성형AI 클라우드에 특화된 고성능·저전력의 NPU(신경망처리장치) 핵심기술을 개발했다고 4일 밝혔다.

연구팀이 제안한 기술은 컴퓨터 아키텍처 분야에서 최고 권위를 자랑하는 국제 학회인 ‘2025 국제 컴퓨터구조 심포지엄(International Symposium on Computer Architecture, ISCA 2025)’에 채택됐다.

이번 연구의 핵심은 추론 과정에서 경량화를 통해 정확도 손실을 최소화하면서도 메모리 병목 문제를 해결해 대규모 생성형AI 서비스의 성능을 개선하는 것이다. 이번 연구는 AI인프라의 핵심 구성요소인 AI반도체와 AI시스템SW를 통합 설계했다는 점에서 그 가치를 높게 인정받았다.

기존 GPU 기반 AI 인프라는 높은 메모리 대역폭과 메모리 용량 요구를 충족하기 위해 다수의 GPU 디바이스가 필요한 반면, 이번 기술은 메모리 사용의 대부분을 차지하는 KV 캐시의 양자화*를 통해 적은 수의 NPU 디바이스만으로 동일 수준의 AI 인프라를 구성할 수 있어, 생성형 AI 클라우드 구축 비용을 크게 절감할 수 있다.

*KV 캐시(Key-Value Cache)의 양자화: 생성형 AI 모델을 작동할 때 성능을 높이기 위해 사용하는 일종의 임시 저장 공간에 데이터 크기를 줄이는 것을 의미(32비트로 저장된 수를 4비트로 바꾸면, 데이터 크기는 1/8로 줄어듬)

연구팀은 기존 NPU 아키텍처의 연산 로직을 변경하지 않으면서 메모리 인터페이스와 통합될 수 있도록 설계했다. 이번 하드웨어 아키텍처 기술은 제안된 양자화 알고리즘을 구현할 뿐만 아니라, 제한된 메모리 대역폭 및 용량을 효율적으로 활용하기 위한 페이지 단위 메모리 관리 기법*과 양자화된 KV 캐시에 최적화된 새로운 인코딩 기법 등을 개발했다.

*페이지 단위 메모리 관리 기법: CPU처럼 메모리 주소를 가상화하여 NPU 내부에서 일관된 방식으로 접근할 수 있게 함

또한, 최신 GPU 대비 비용·전력 효율성이 우수한 NPU 기반 AI 클라우드를 구성할 경우, NPU의 고성능, 저전력 특성을 활용해 운영 비용 역시 크게 절감할 수 있을 것으로 기대된다.

박종세 교수는 “이 연구는 (주)하이퍼엑셀과의 공동연구를 통해 생성형AI 추론 경량화 알고리즘에서 그 해법을 찾았고 ‘메모리 문제’를 해결할 수 있는 NPU 핵심기술 개발에 성공했다. 이 기술을 통해 추론의 정확도를 유지하면서 메모리 요구량을 줄이는 경량화 기법과, 이에 최적화된 하드웨어 설계를 결합해 최신 GPU 대비 평균 60% 이상 성능이 향상된 NPU를 구현했다” 고 말했다.

이어 “이 기술은 생성형AI에 특화된 고성능·저전력 인프라 구현 가능성을 입증했으며, AI클라우드 데이터센터뿐 아니라 능동적인 실행형 AI인 ‘에이전틱 AI ’등으로 대표되는 AI 대전환(AX) 환경에서도 핵심 역할이 기대된다”고 강조했다.

이 연구는 김민수 박사과정 학생과 ㈜하이퍼엑셀 홍성민 박사가 공동 제1 저자로 지난 6월 21일부터 6월 25일까지 일본 도쿄에서 열린 ‘2025 국제 컴퓨터구조 심포지엄(ISCA)’에 발표됐다. 국제적 저명학회인 ISCA는 올해는 570편의 논문이 제출됐으며 그중 127편 만이 채택됐다. (채택률 22.7%).

※논문 제목: Oaken: Fast and Efficient LLM Serving with Online-Offline Hybrid KV Cache Quantization

※DOI: https://doi.org/10.1145/3695053.3731019

한편 이번 연구는 한국연구재단 우수신진연구자지원사업, 정보통신기획평가원(IITP), 인공지능반도체대학원지원사업의 지원을 받아 수행됐다.

2025.07.04 조회수 855

60% 이상 챗GPT 추론 성능 향상할 NPU 핵심기술 개발

오픈AI 챗GPT4, 구글 Gemnini 2.5 등 최신 생성형AI 모델들은 높은 메모리 대역폭(Bandwidth) 뿐만 아니라 많은 메모리 용량(Capacity)를 필요로 한다. 마이크로소프트, 구글 등 생성형AI 클라우드 운영 기업들이 엔비디아 GPU를 수십만 장씩 구매하는 이유다. 이런 고성능 AI 인프라 구축의 핵심 난제를 해소할 방안으로, 한국 연구진이 최신 GPU 대비 약 44% 낮은 전력 소모에도 평균 60% 이상 생성형 AI 모델의 추론 성능을 향상할 NPU(신경망처리장치)* 핵심 기술을 개발하는데 성공했다.

*NPU(Neural Processing Unit): 인공신경망(Neural Network)을 빠르게 처리하기 위해 만든 AI 전용 반도체 칩

우리 대학 전산학부 박종세 교수 연구팀과 (주)하이퍼엑셀(전기및전자공학부 김주영 교수 창업기업)이 연구 협력을 통해, 챗GPT와 같은 생성형AI 클라우드에 특화된 고성능·저전력의 NPU(신경망처리장치) 핵심기술을 개발했다고 4일 밝혔다.

연구팀이 제안한 기술은 컴퓨터 아키텍처 분야에서 최고 권위를 자랑하는 국제 학회인 ‘2025 국제 컴퓨터구조 심포지엄(International Symposium on Computer Architecture, ISCA 2025)’에 채택됐다.

이번 연구의 핵심은 추론 과정에서 경량화를 통해 정확도 손실을 최소화하면서도 메모리 병목 문제를 해결해 대규모 생성형AI 서비스의 성능을 개선하는 것이다. 이번 연구는 AI인프라의 핵심 구성요소인 AI반도체와 AI시스템SW를 통합 설계했다는 점에서 그 가치를 높게 인정받았다.

기존 GPU 기반 AI 인프라는 높은 메모리 대역폭과 메모리 용량 요구를 충족하기 위해 다수의 GPU 디바이스가 필요한 반면, 이번 기술은 메모리 사용의 대부분을 차지하는 KV 캐시의 양자화*를 통해 적은 수의 NPU 디바이스만으로 동일 수준의 AI 인프라를 구성할 수 있어, 생성형 AI 클라우드 구축 비용을 크게 절감할 수 있다.

*KV 캐시(Key-Value Cache)의 양자화: 생성형 AI 모델을 작동할 때 성능을 높이기 위해 사용하는 일종의 임시 저장 공간에 데이터 크기를 줄이는 것을 의미(32비트로 저장된 수를 4비트로 바꾸면, 데이터 크기는 1/8로 줄어듬)

연구팀은 기존 NPU 아키텍처의 연산 로직을 변경하지 않으면서 메모리 인터페이스와 통합될 수 있도록 설계했다. 이번 하드웨어 아키텍처 기술은 제안된 양자화 알고리즘을 구현할 뿐만 아니라, 제한된 메모리 대역폭 및 용량을 효율적으로 활용하기 위한 페이지 단위 메모리 관리 기법*과 양자화된 KV 캐시에 최적화된 새로운 인코딩 기법 등을 개발했다.

*페이지 단위 메모리 관리 기법: CPU처럼 메모리 주소를 가상화하여 NPU 내부에서 일관된 방식으로 접근할 수 있게 함

또한, 최신 GPU 대비 비용·전력 효율성이 우수한 NPU 기반 AI 클라우드를 구성할 경우, NPU의 고성능, 저전력 특성을 활용해 운영 비용 역시 크게 절감할 수 있을 것으로 기대된다.

박종세 교수는 “이 연구는 (주)하이퍼엑셀과의 공동연구를 통해 생성형AI 추론 경량화 알고리즘에서 그 해법을 찾았고 ‘메모리 문제’를 해결할 수 있는 NPU 핵심기술 개발에 성공했다. 이 기술을 통해 추론의 정확도를 유지하면서 메모리 요구량을 줄이는 경량화 기법과, 이에 최적화된 하드웨어 설계를 결합해 최신 GPU 대비 평균 60% 이상 성능이 향상된 NPU를 구현했다” 고 말했다.

이어 “이 기술은 생성형AI에 특화된 고성능·저전력 인프라 구현 가능성을 입증했으며, AI클라우드 데이터센터뿐 아니라 능동적인 실행형 AI인 ‘에이전틱 AI ’등으로 대표되는 AI 대전환(AX) 환경에서도 핵심 역할이 기대된다”고 강조했다.

이 연구는 김민수 박사과정 학생과 ㈜하이퍼엑셀 홍성민 박사가 공동 제1 저자로 지난 6월 21일부터 6월 25일까지 일본 도쿄에서 열린 ‘2025 국제 컴퓨터구조 심포지엄(ISCA)’에 발표됐다. 국제적 저명학회인 ISCA는 올해는 570편의 논문이 제출됐으며 그중 127편 만이 채택됐다. (채택률 22.7%).

※논문 제목: Oaken: Fast and Efficient LLM Serving with Online-Offline Hybrid KV Cache Quantization

※DOI: https://doi.org/10.1145/3695053.3731019

한편 이번 연구는 한국연구재단 우수신진연구자지원사업, 정보통신기획평가원(IITP), 인공지능반도체대학원지원사업의 지원을 받아 수행됐다.

2025.07.04 조회수 855 -

최신현 교수, 올해의 현우 KAIST 학술상 수상

우리 대학 전기및전자공학부 최신현 교수가 차세대 AI 하드웨어 개발 및 혁신적인 반도체 관련 연구 성과로, KAIST가 주관하고 현우문화재단(이사장 곽수일)이 후원하는 `현우 KAIST 학술상' 수상자로 선정됐다.

수상자로 선정된 최신현 교수의 중점 연구 분야는 미래형 메모리와 컴퓨터 장치 개발에 집중한 ▶저항 스위칭 소자(resistive switching device)를 이용해 기본 방식보다 더 빠르고 효율적인 차세대 메모리·컴퓨팅 장치 개발, ▶엣지 컴퓨팅(edge computing)과 뉴로모픽 컴퓨팅(neuromorphic computing)의 스마트한 컴퓨터 메모리 기능 등 통합 시스템 응용, ▶기존 3단자 트랜지스터(3-terminal transistor) 방식과 다른 더 효율적이고 창의적인 컴퓨팅·메모리 소자 작동 방식 개발이다.

대표적인 연구 업적으로 차세대 메모리 기술 분야에서 기존의 값비싼 초미세 노광공정*을 사용하는 방식보다 전기를 15배 이상 절감하고, 수직 적층 구조에 최적화된 초저전력 차세대 상변화 메모리(phase-change memory) 소자 개발에 성공하였다.

* 노광공정: 반도체 칩 위에 미세한 회로 패턴을 실리콘 웨이퍼 위에 새기는 공정으로 고급기술이고 비용이 많이 드는 단점이 있음

나아가, 최 교수는 차세대 메모리·컴퓨팅 소자를 기반으로, 기존의 CPU, GPU와 같이 많은 전력을 쓰는 칩을 대체할 수 있는 AI 알고리즘을 효율적으로 구동하는 차세대 컴퓨팅 하드웨어(칩)를 개발하였다. 이를 통해 데이터를 더 빠르고 효율적으로 작동시키며 스마트폰, 자율주행 등 다양한 응용하여 실생활에 활용 가능한 주목할 만한 성과를 거두었다.

또한 메모리 소자의 동작 원리를 기초 물리법칙에 기반한 원자단위까지 분석함으로써 이를 통해 메모리 성능을 더 빠르고 안정적으로 향상시킬 방법을 제시하는데 크게 기여하였다.

최 교수의 연구는 재료 분석부터 반도체 소자, 통합 시스템 개발 등 반도체 기술 전 과정에 대한 연구 분야를 아우르며, 그 성과는 네이처(Nature), 네이처 일렉트로닉스(Nature Electronics), 네이처 커뮤니케이션스(Nature Communications), 사이언스 어드밴시스(Science Advances) 등 최상위 저널에 게재되는 등 특출한 성과를 보여주었다.

최신현 교수는 “최근 큰 사회적 변화를 주도하고 있는 IT와 인공지능 관련 하드웨어 연구로 뜻깊은 상을 받게 되어서 영광이고, 이번 연구를 통해 학계와 기업에 새로운 시각을 제공할 수 있어 감회가 깊다.”며, “앞으로도 후속 연구자들에게 영감을 주며 실제로 사회에 기여할 수 있는 연구 성과가 나올 수 있도록 끊임없이 노력하겠다”고 향후 포부를 밝혔다.

한편, 올해로 5회째 시행되는 `현우 KAIST 학술상'은 KAIST에서 우수한 학술적 업적을 남긴 학자들을 매년 포상하고자 현우문화재단 곽수일 이사장이 기부한 재원을 바탕으로 제정된 상이다.

현우재단 선정위원과 KAIST 교원 포상 추천위원회의 엄격한 심사를 거쳐, 탁월한 학술 업적을 이룬 교원 1명을 매년 선정해 상패와 함께 1천만 원의 포상금을 수여하고 있다. 올해 시상식은 30일 오전 10시 KAIST 학술문화관 정근모 홀에서 개최되었다.

2025.05.02 조회수 1890

최신현 교수, 올해의 현우 KAIST 학술상 수상

우리 대학 전기및전자공학부 최신현 교수가 차세대 AI 하드웨어 개발 및 혁신적인 반도체 관련 연구 성과로, KAIST가 주관하고 현우문화재단(이사장 곽수일)이 후원하는 `현우 KAIST 학술상' 수상자로 선정됐다.

수상자로 선정된 최신현 교수의 중점 연구 분야는 미래형 메모리와 컴퓨터 장치 개발에 집중한 ▶저항 스위칭 소자(resistive switching device)를 이용해 기본 방식보다 더 빠르고 효율적인 차세대 메모리·컴퓨팅 장치 개발, ▶엣지 컴퓨팅(edge computing)과 뉴로모픽 컴퓨팅(neuromorphic computing)의 스마트한 컴퓨터 메모리 기능 등 통합 시스템 응용, ▶기존 3단자 트랜지스터(3-terminal transistor) 방식과 다른 더 효율적이고 창의적인 컴퓨팅·메모리 소자 작동 방식 개발이다.

대표적인 연구 업적으로 차세대 메모리 기술 분야에서 기존의 값비싼 초미세 노광공정*을 사용하는 방식보다 전기를 15배 이상 절감하고, 수직 적층 구조에 최적화된 초저전력 차세대 상변화 메모리(phase-change memory) 소자 개발에 성공하였다.

* 노광공정: 반도체 칩 위에 미세한 회로 패턴을 실리콘 웨이퍼 위에 새기는 공정으로 고급기술이고 비용이 많이 드는 단점이 있음

나아가, 최 교수는 차세대 메모리·컴퓨팅 소자를 기반으로, 기존의 CPU, GPU와 같이 많은 전력을 쓰는 칩을 대체할 수 있는 AI 알고리즘을 효율적으로 구동하는 차세대 컴퓨팅 하드웨어(칩)를 개발하였다. 이를 통해 데이터를 더 빠르고 효율적으로 작동시키며 스마트폰, 자율주행 등 다양한 응용하여 실생활에 활용 가능한 주목할 만한 성과를 거두었다.

또한 메모리 소자의 동작 원리를 기초 물리법칙에 기반한 원자단위까지 분석함으로써 이를 통해 메모리 성능을 더 빠르고 안정적으로 향상시킬 방법을 제시하는데 크게 기여하였다.

최 교수의 연구는 재료 분석부터 반도체 소자, 통합 시스템 개발 등 반도체 기술 전 과정에 대한 연구 분야를 아우르며, 그 성과는 네이처(Nature), 네이처 일렉트로닉스(Nature Electronics), 네이처 커뮤니케이션스(Nature Communications), 사이언스 어드밴시스(Science Advances) 등 최상위 저널에 게재되는 등 특출한 성과를 보여주었다.

최신현 교수는 “최근 큰 사회적 변화를 주도하고 있는 IT와 인공지능 관련 하드웨어 연구로 뜻깊은 상을 받게 되어서 영광이고, 이번 연구를 통해 학계와 기업에 새로운 시각을 제공할 수 있어 감회가 깊다.”며, “앞으로도 후속 연구자들에게 영감을 주며 실제로 사회에 기여할 수 있는 연구 성과가 나올 수 있도록 끊임없이 노력하겠다”고 향후 포부를 밝혔다.

한편, 올해로 5회째 시행되는 `현우 KAIST 학술상'은 KAIST에서 우수한 학술적 업적을 남긴 학자들을 매년 포상하고자 현우문화재단 곽수일 이사장이 기부한 재원을 바탕으로 제정된 상이다.

현우재단 선정위원과 KAIST 교원 포상 추천위원회의 엄격한 심사를 거쳐, 탁월한 학술 업적을 이룬 교원 1명을 매년 선정해 상패와 함께 1천만 원의 포상금을 수여하고 있다. 올해 시상식은 30일 오전 10시 KAIST 학술문화관 정근모 홀에서 개최되었다.

2025.05.02 조회수 1890 -

고성능 촉매 개발, 반도체 핫전자 기술을 통해 해결하다

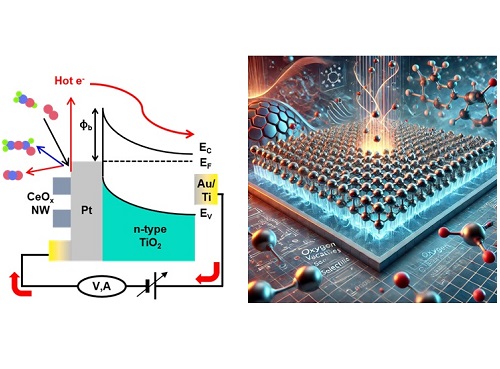

우리 대학 화학과 박정영 석좌교수, 신소재공학과 정연식 교수, 그리고 KIST 김동훈 박사 공동 연구팀이 반도체 기술을 활용하여 촉매 성능에 특정 변인이 미치는 영향을 정량적으로 분석할 수 있는 새로운 플랫폼을 성공적으로 구현했다. 이를 통해 대표적인 다경로 화학 반응인 메탄올 산화 반응에서 메틸 포르메이트 선택성을 크게 향상시켰으며, 이번 연구는 차세대 고성능 이종 촉매 개발을 앞당기는 데 기여할 것으로 기대된다고 1일 밝혔다.

다경로 화학 반응에서는 반응성과 선택성의 상충 관계로 인해 특정 생성물의 선택성을 높이는 것이 어려운 문제로 남아 있다. 특히, 메탄올 산화 반응에서는 이산화탄소와 더불어 고부가 가치 생성물인 메틸 포르메이트가 생성되므로, 메틸 포르메이트의 선택성을 극대화하는 것이 중요하다.

그러나 기존 불규칙적인 구조의 이종 촉매에서는 금속-산화물 계면 밀도를 비롯한 여러 변인이 동시에 촉매 성능에 영향을 미치기 때문에 특정 변수가 개별적으로 미치는 영향을 분석하는 것이 어렵다. 이에 KAIST-KIST 공동 연구팀은 균일하게 정렬된 금속산화물 나노 패턴을 구현할 수 있는 반도체 기술을 활용하여 이종 촉매 성능에 영향을 미칠 수 있는 다른 변인을 통제하고, 오로지 금속산화물의 물성만이 촉매 성능에 미치는 영향을 정량적으로 분석하였다. 구체적으로, 산소 공극 (Oxygen Vacancy)의 양을 조절하기 위해 다양한 환경에서 열처리한 세륨 산화물 (CeOx) 나노 패턴을 제작하고, 이를 백금(Pt) 박막 촉매 위에 전사하여 금속산화물의 산소 공극이 메틸 포르메이트 선택성에 미치는 영향을 분석했다.

연구 결과, 산소 공극이 가장 풍부하게 생성된 진공 환경에서 열처리한 CeOx-Pt 이종 촉매의 경우, 열처리를 하지 않은 CeO2-Pt 이종 촉매 대비 약 50% 향상된 메틸 포르메이트 선택성을 보였으며, 이는 반응 중 발생하는 핫 전자의 검출을 통해 실시간으로도 확인되었다. 또한, 연구팀은 양자역학 기반의 DFT 시뮬레이션을 통해 금속산화물 내부의 산소 공극이 이종 촉매의 성능에 미치는 영향을 이론적으로 규명하였다. 시뮬레이션 결과, 산소 공극은 금속/산화물 계면에 많은 양의 전자를 축적시키면서 반응 중간체 간 결합을 촉진하였고, 이로 인해 메틸 포르메이트 선택성이 향상됨을 확인하였다.

이에 대해 박정영 교수는 “이번에 개발한 반도체기반 플랫폼을 통해 핫전하와 촉매 선택성의 정량적 분석이 가능해짐에 따라 핫전하 기반의 광촉매 센서의 상용화 개발 및 핫전하 기반 광열촉매 시스템의 상용화 개발로 이어질 수 있다.”고 언급했다. 신소재공학과 정연식 교수는 “기존의 무작위 구조를 가진 촉매에서는 특정 변수의 영향을 정량적으로 분석하는 것이 어려웠으나, 반도체 기술을 활용한 이번 연구를 통해 보다 효율적인 이종 촉매 설계와 선택성 조절 전략을 제시할 수 있을 것으로 기대된다”고 밝혔다.

신소재공학과 이규락 박사, 화학과 송경재 박사, KIST 홍두선 박사가 공동 제 1 저자로 참여한 이번 연구는 국제학술지 ‘네이처 커뮤니케이션스 (Nature Communications)’에 3월 25일 자로 온라인 게재됐다. (논문 제목: Unraveling Oxygen Vacancy-Driven Catalytic Selectivity and Hot Electron Generation on Heterointerfaces using Nanostructured Platform)

이번 연구는 산업통상자원부 에너지혁신인재양성사업, 과학기술정보통신부 중견연구자지원사업, 그리고 과학기술정보통신부 국가전략기술소재개발사업 등의 지원을 받아 수행됐다.

2025.04.01 조회수 3988

고성능 촉매 개발, 반도체 핫전자 기술을 통해 해결하다

우리 대학 화학과 박정영 석좌교수, 신소재공학과 정연식 교수, 그리고 KIST 김동훈 박사 공동 연구팀이 반도체 기술을 활용하여 촉매 성능에 특정 변인이 미치는 영향을 정량적으로 분석할 수 있는 새로운 플랫폼을 성공적으로 구현했다. 이를 통해 대표적인 다경로 화학 반응인 메탄올 산화 반응에서 메틸 포르메이트 선택성을 크게 향상시켰으며, 이번 연구는 차세대 고성능 이종 촉매 개발을 앞당기는 데 기여할 것으로 기대된다고 1일 밝혔다.

다경로 화학 반응에서는 반응성과 선택성의 상충 관계로 인해 특정 생성물의 선택성을 높이는 것이 어려운 문제로 남아 있다. 특히, 메탄올 산화 반응에서는 이산화탄소와 더불어 고부가 가치 생성물인 메틸 포르메이트가 생성되므로, 메틸 포르메이트의 선택성을 극대화하는 것이 중요하다.

그러나 기존 불규칙적인 구조의 이종 촉매에서는 금속-산화물 계면 밀도를 비롯한 여러 변인이 동시에 촉매 성능에 영향을 미치기 때문에 특정 변수가 개별적으로 미치는 영향을 분석하는 것이 어렵다. 이에 KAIST-KIST 공동 연구팀은 균일하게 정렬된 금속산화물 나노 패턴을 구현할 수 있는 반도체 기술을 활용하여 이종 촉매 성능에 영향을 미칠 수 있는 다른 변인을 통제하고, 오로지 금속산화물의 물성만이 촉매 성능에 미치는 영향을 정량적으로 분석하였다. 구체적으로, 산소 공극 (Oxygen Vacancy)의 양을 조절하기 위해 다양한 환경에서 열처리한 세륨 산화물 (CeOx) 나노 패턴을 제작하고, 이를 백금(Pt) 박막 촉매 위에 전사하여 금속산화물의 산소 공극이 메틸 포르메이트 선택성에 미치는 영향을 분석했다.

연구 결과, 산소 공극이 가장 풍부하게 생성된 진공 환경에서 열처리한 CeOx-Pt 이종 촉매의 경우, 열처리를 하지 않은 CeO2-Pt 이종 촉매 대비 약 50% 향상된 메틸 포르메이트 선택성을 보였으며, 이는 반응 중 발생하는 핫 전자의 검출을 통해 실시간으로도 확인되었다. 또한, 연구팀은 양자역학 기반의 DFT 시뮬레이션을 통해 금속산화물 내부의 산소 공극이 이종 촉매의 성능에 미치는 영향을 이론적으로 규명하였다. 시뮬레이션 결과, 산소 공극은 금속/산화물 계면에 많은 양의 전자를 축적시키면서 반응 중간체 간 결합을 촉진하였고, 이로 인해 메틸 포르메이트 선택성이 향상됨을 확인하였다.

이에 대해 박정영 교수는 “이번에 개발한 반도체기반 플랫폼을 통해 핫전하와 촉매 선택성의 정량적 분석이 가능해짐에 따라 핫전하 기반의 광촉매 센서의 상용화 개발 및 핫전하 기반 광열촉매 시스템의 상용화 개발로 이어질 수 있다.”고 언급했다. 신소재공학과 정연식 교수는 “기존의 무작위 구조를 가진 촉매에서는 특정 변수의 영향을 정량적으로 분석하는 것이 어려웠으나, 반도체 기술을 활용한 이번 연구를 통해 보다 효율적인 이종 촉매 설계와 선택성 조절 전략을 제시할 수 있을 것으로 기대된다”고 밝혔다.

신소재공학과 이규락 박사, 화학과 송경재 박사, KIST 홍두선 박사가 공동 제 1 저자로 참여한 이번 연구는 국제학술지 ‘네이처 커뮤니케이션스 (Nature Communications)’에 3월 25일 자로 온라인 게재됐다. (논문 제목: Unraveling Oxygen Vacancy-Driven Catalytic Selectivity and Hot Electron Generation on Heterointerfaces using Nanostructured Platform)

이번 연구는 산업통상자원부 에너지혁신인재양성사업, 과학기술정보통신부 중견연구자지원사업, 그리고 과학기술정보통신부 국가전략기술소재개발사업 등의 지원을 받아 수행됐다.

2025.04.01 조회수 3988 -

인공지능반도체대학원, 제2회 한국인공지능시스템포럼 AI 산업혁신 논의

우리 대학 인공지능반도체대학원 주최로 20일(목) 오전 대전 오노마 호텔에서 ‘제2회 한국인공지능시스템포럼(KAISF) 조찬 강연회’가 성황리에 개최되었다.

본 행사는 인공지능(AI) 기술의 최신 동향과 혁신 및 응용, 특히 AI-X(AI-특정산업)에 대해 다양한 분야의 전문가들이 모여 심도 있는 논의를 진행하는 자리로 LG AI 연구원의 최정규 상무가 LLM(거대언어모델)에 대해 개발에 대해 발표한다.

조찬 회의에는 총 65명의 AI 전문가가 참석하였으며, LG AI 연구원에서 최근 개발하고 공개한 대규모 언어 모델인 ‘엑사원(EXAONE)에 대해 Driving the Future of AI Innovation’라는 주제로 발제 발표가 진행되었다.

최정규 LG AI 연구원 상무는 LG 엑사원의 현재 연구 현황과 향후 글로벌 AI 시장에서의 계획을 발표하였으며 특히 최근 AI 생태계를 뜨겁게 달구고 있는 ‘딥시크(Deepseek)’를 중심으로, 글로벌 AI 경쟁 속에서 한국 AI 기업이 나아가야 할 방향과 기회에 대해 논의하였다.

이번 강연회에서는 LLM 기술의 산업적 적용 가능성도 주요 의제로 다뤄졌다. 전문가들은 LLM 기술이 금융, 의료, 제조, 국방 및 교육 등 다양한 사업에서 어떻게 활용될 수 있는지를 논의하며, 실제 적응 사례도 공유했다.

유회준 인공지능반도체대학원장 겸 한국인공지능시스템포럼 의장은“이번 강연회를 통해 대전을 중심으로 AI에 의한 산업전환 (AI-X)이 주도되고 이들의 적용 사례가 전국적으로 공유되면 좋겠다”며 산학연 협력을 강화하는데 주력하자고 말했다.

한국인공지능시스템포럼은 앞으로도 지속적으로 포럼과 프로그램을 운영하며 AI-X을 통한 한국 산업 혁신을 선도하는 중심 허브로 자리매김할 계획임을 밝혔다. 또한, 대전을 중심으로 한국의 모든 연구자 및 산업 관계자들이 정보를 공유하고 협력할 수 있도록 지원할 예정이다.

2025.03.20 조회수 2393

인공지능반도체대학원, 제2회 한국인공지능시스템포럼 AI 산업혁신 논의

우리 대학 인공지능반도체대학원 주최로 20일(목) 오전 대전 오노마 호텔에서 ‘제2회 한국인공지능시스템포럼(KAISF) 조찬 강연회’가 성황리에 개최되었다.

본 행사는 인공지능(AI) 기술의 최신 동향과 혁신 및 응용, 특히 AI-X(AI-특정산업)에 대해 다양한 분야의 전문가들이 모여 심도 있는 논의를 진행하는 자리로 LG AI 연구원의 최정규 상무가 LLM(거대언어모델)에 대해 개발에 대해 발표한다.

조찬 회의에는 총 65명의 AI 전문가가 참석하였으며, LG AI 연구원에서 최근 개발하고 공개한 대규모 언어 모델인 ‘엑사원(EXAONE)에 대해 Driving the Future of AI Innovation’라는 주제로 발제 발표가 진행되었다.

최정규 LG AI 연구원 상무는 LG 엑사원의 현재 연구 현황과 향후 글로벌 AI 시장에서의 계획을 발표하였으며 특히 최근 AI 생태계를 뜨겁게 달구고 있는 ‘딥시크(Deepseek)’를 중심으로, 글로벌 AI 경쟁 속에서 한국 AI 기업이 나아가야 할 방향과 기회에 대해 논의하였다.

이번 강연회에서는 LLM 기술의 산업적 적용 가능성도 주요 의제로 다뤄졌다. 전문가들은 LLM 기술이 금융, 의료, 제조, 국방 및 교육 등 다양한 사업에서 어떻게 활용될 수 있는지를 논의하며, 실제 적응 사례도 공유했다.

유회준 인공지능반도체대학원장 겸 한국인공지능시스템포럼 의장은“이번 강연회를 통해 대전을 중심으로 AI에 의한 산업전환 (AI-X)이 주도되고 이들의 적용 사례가 전국적으로 공유되면 좋겠다”며 산학연 협력을 강화하는데 주력하자고 말했다.

한국인공지능시스템포럼은 앞으로도 지속적으로 포럼과 프로그램을 운영하며 AI-X을 통한 한국 산업 혁신을 선도하는 중심 허브로 자리매김할 계획임을 밝혔다. 또한, 대전을 중심으로 한국의 모든 연구자 및 산업 관계자들이 정보를 공유하고 협력할 수 있도록 지원할 예정이다.

2025.03.20 조회수 2393 -

최대 11배 빨라진 PIM 반도체 네트워크 개발

최근 인공지능, 빅데이터, 생명과학 등 연구에 사용되는 메모리 대역폭이 차지하는 비중이 높아, 메모리 내부에 연산장치를 배치하는 프로세싱-인-메모리(Processing-in-Memory, 이하 PIM) 반도체에 대한 연구개발이 활발히 진행되고 있다. 국제 공동 연구진이 기존의 PIM 반도체가 내부장치를 활용하면서도 통신을 할때 반드시 PIM 반도체 외부로 연결되는 CPU를 통해야한다는 문제점으로 발생한 병목현상을 해결했다.

우리 대학 전기및전자공학부 김동준 교수 연구팀이 미국 노스이스턴 대학(Northeastern Univ.), 보스턴 대학(Boston Univ.)와 스페인 무르시아 대학(Universidad de Murcia)의 저명 연구진과‘PIM 반도체 간 집합 통신에 특화된 인터커넥션 네트워크 아키텍처’를 통한 공동연구로 PIM 반도체의 통신 성능을 비약적으로 향상하는 기법을 개발했다고 19일 밝혔다.

김동준 교수 연구팀은 기존 PIM 반도체가 갖는 메모리 내부 연산 장치 간 통신 구조의 한계를 밝히고, 기존에 메모리 내부에 존재하는 데이터 이동을 위한 버스 구조를 최대한 활용하면서 각 연산장치를 직접적으로 상호 연결하는 *인터커넥션 네트워크 구조를 적용함으로써 PIM 반도체의 통신 성능을 극대화하는 기법을 제안했다.

※ 인터커넥션 네트워크(interconnection network): 다중 연산 장치를 포함하는 대규모 시스템 설계에 쓰이는 연산 장치 간 연결 구조를 말한다. 인터커넥션 네트워크는 다중 연산 장치를 포함하는 시스템 설계의 필수 요소 중 하나로써 시스템 규모가 커질수록 더욱 중요해지는 특징이 있다.

이를 통해 PIM 반도체를 위한 연산 과정에서 통신 처리를 위한 CPU의 개입을 최소화해 PIM 반도체 시스템의 전체적인 성능과 활용성을 높인 PIM 반도체에 특화된 인터커넥션 네트워크 구조를 개발했다.

메모리 공정은 복잡한 로직의 추가가 어렵다는 문제점이 있는데 김동준 교수팀이 개발한 네트워크 구조는 PIM에서 비용 효율적인 인터커넥트를 구현했다.

이 구조는 병렬 컴퓨팅과 기계학습 분야에서 널리 활용되는 집합 통신(Collective communication) 패턴에 특화돼 있으며, 각 연산장치의 통신량과 데이터 이동 경로를 미리 파악할 수 있다는 집합 통신의 결정성(determinism) 특징을 활용해 기존 네트워크에서 비용을 발생시키는 주요 구성 요소들을 최소화시켰다.

기존 PIM 반도체들이 통신하기 위해서는 CPU를 거쳐야만 하기 때문에 상당한 성능 손실이 있었다. 하지만, 연구팀은 PIM 특화 인터커넥션 네트워크를 적용하면 기존 시스템 대비 어플리케이션 성능을 최대 11배 향상했다고 밝혔다. 그 이유는 PIM 반도체의 내부 메모리 대역폭 활용률을 극대화하고 PIM 메모리 시스템의 규모가 커짐에 따라 통신 성능의 확장성이 함께 증가했기 때문이다.

최근 미국 전기전자공학회(IEEE) 컴퓨터 아키텍쳐 분야에서는 한국 최초로 2025 IEEE 펠로우(석학회원)로 선임되었고 이 연구를 주도한 김동준 교수는 “데이터 이동(data movement)을 줄이는 것은 PIM을 포함한 모든 시스템 반도체에서 핵심적인 요소이며, PIM은 컴퓨팅 시스템의 성능과 효율성을 향상할 수 있지만 PIM 연산장치 간 데이터 이동으로 인해 성능 확장성이 제약될 수 있어 응용 분야가 제한적이고, PIM 인터커넥트가 이에 대한 해법이 될 수 있다”고 연구의 의의를 설명했다.

전기및전자공학부 손효준 박사과정이 제1 저자로 참여한 이번 연구는 미국 네바다주 라스베이거스에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 ‘2025 IEEE International Symposium on High Performance Computer Architecture, HPCA 2025’에서 올 3월에 발표될 예정이다. (논문명: PIMnet: A Domain-Specific Network for Efficient Collective Communication in Scalable PIM)

한편 이번 연구는 한국연구재단, 삼성전자, 정보통신기획평가원 차세대지능형반도체기술개발사업의 지원을 받아 수행됐다.

2025.02.19 조회수 4007

최대 11배 빨라진 PIM 반도체 네트워크 개발

최근 인공지능, 빅데이터, 생명과학 등 연구에 사용되는 메모리 대역폭이 차지하는 비중이 높아, 메모리 내부에 연산장치를 배치하는 프로세싱-인-메모리(Processing-in-Memory, 이하 PIM) 반도체에 대한 연구개발이 활발히 진행되고 있다. 국제 공동 연구진이 기존의 PIM 반도체가 내부장치를 활용하면서도 통신을 할때 반드시 PIM 반도체 외부로 연결되는 CPU를 통해야한다는 문제점으로 발생한 병목현상을 해결했다.

우리 대학 전기및전자공학부 김동준 교수 연구팀이 미국 노스이스턴 대학(Northeastern Univ.), 보스턴 대학(Boston Univ.)와 스페인 무르시아 대학(Universidad de Murcia)의 저명 연구진과‘PIM 반도체 간 집합 통신에 특화된 인터커넥션 네트워크 아키텍처’를 통한 공동연구로 PIM 반도체의 통신 성능을 비약적으로 향상하는 기법을 개발했다고 19일 밝혔다.

김동준 교수 연구팀은 기존 PIM 반도체가 갖는 메모리 내부 연산 장치 간 통신 구조의 한계를 밝히고, 기존에 메모리 내부에 존재하는 데이터 이동을 위한 버스 구조를 최대한 활용하면서 각 연산장치를 직접적으로 상호 연결하는 *인터커넥션 네트워크 구조를 적용함으로써 PIM 반도체의 통신 성능을 극대화하는 기법을 제안했다.

※ 인터커넥션 네트워크(interconnection network): 다중 연산 장치를 포함하는 대규모 시스템 설계에 쓰이는 연산 장치 간 연결 구조를 말한다. 인터커넥션 네트워크는 다중 연산 장치를 포함하는 시스템 설계의 필수 요소 중 하나로써 시스템 규모가 커질수록 더욱 중요해지는 특징이 있다.

이를 통해 PIM 반도체를 위한 연산 과정에서 통신 처리를 위한 CPU의 개입을 최소화해 PIM 반도체 시스템의 전체적인 성능과 활용성을 높인 PIM 반도체에 특화된 인터커넥션 네트워크 구조를 개발했다.

메모리 공정은 복잡한 로직의 추가가 어렵다는 문제점이 있는데 김동준 교수팀이 개발한 네트워크 구조는 PIM에서 비용 효율적인 인터커넥트를 구현했다.

이 구조는 병렬 컴퓨팅과 기계학습 분야에서 널리 활용되는 집합 통신(Collective communication) 패턴에 특화돼 있으며, 각 연산장치의 통신량과 데이터 이동 경로를 미리 파악할 수 있다는 집합 통신의 결정성(determinism) 특징을 활용해 기존 네트워크에서 비용을 발생시키는 주요 구성 요소들을 최소화시켰다.

기존 PIM 반도체들이 통신하기 위해서는 CPU를 거쳐야만 하기 때문에 상당한 성능 손실이 있었다. 하지만, 연구팀은 PIM 특화 인터커넥션 네트워크를 적용하면 기존 시스템 대비 어플리케이션 성능을 최대 11배 향상했다고 밝혔다. 그 이유는 PIM 반도체의 내부 메모리 대역폭 활용률을 극대화하고 PIM 메모리 시스템의 규모가 커짐에 따라 통신 성능의 확장성이 함께 증가했기 때문이다.

최근 미국 전기전자공학회(IEEE) 컴퓨터 아키텍쳐 분야에서는 한국 최초로 2025 IEEE 펠로우(석학회원)로 선임되었고 이 연구를 주도한 김동준 교수는 “데이터 이동(data movement)을 줄이는 것은 PIM을 포함한 모든 시스템 반도체에서 핵심적인 요소이며, PIM은 컴퓨팅 시스템의 성능과 효율성을 향상할 수 있지만 PIM 연산장치 간 데이터 이동으로 인해 성능 확장성이 제약될 수 있어 응용 분야가 제한적이고, PIM 인터커넥트가 이에 대한 해법이 될 수 있다”고 연구의 의의를 설명했다.

전기및전자공학부 손효준 박사과정이 제1 저자로 참여한 이번 연구는 미국 네바다주 라스베이거스에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 ‘2025 IEEE International Symposium on High Performance Computer Architecture, HPCA 2025’에서 올 3월에 발표될 예정이다. (논문명: PIMnet: A Domain-Specific Network for Efficient Collective Communication in Scalable PIM)

한편 이번 연구는 한국연구재단, 삼성전자, 정보통신기획평가원 차세대지능형반도체기술개발사업의 지원을 받아 수행됐다.

2025.02.19 조회수 4007 -

김정호 교수, 한국반도체학술대회 ‘2025 강대원 상’ 수상

우리 대학 전기및전자공학부 김정호 교수가 회로·시스템 분야 '2025년 강대원 상'을 한국반도체학술대회 상임운영위원회로부터 수상한다. 김 교수는 HBM 개발에 기여한 공로를 인정받아 SK하이닉스 이강욱 부사장과 함께 수상한다. 시상식은 13일 오후 강원도 하이원그랜드호텔에서 한국반도체산업협회 · 한국반도체연구조합 · DB하이텍이 공동으로 주관, 개최하는 ‘제32회 한국반도체학술대회(KCS 2025)’ 개막식에서 진행된다.

강대원 상은 세계 최초로 모스펫(MOSFET)과 플로팅게이트를 개발해, 반도체 기술 발전에 신기원을 이룩한 고(故) 강대원 박사를 기리기 위해 제정되었으며, 한국반도체학술대회 상임운영위원회가 지난 2017년 열린 제24회 반도체 학술대회부터 강대원 박사를 이을 인재들을 발굴, 선정해서 시상하고 있다.

김정호 교수는 ‘HBM 아버지’로 불리는 인공지능 반도체 분야의 세계적 권위자이다. 지난 20년 이상 HBM 관련 설계 기술을 세계적으로 주도해 왔다. 특히 HBM 실리콘관통전극(TSV), 인터포저, 신호선 설계(SI), 전력선 설계(PI) 등을 연구하며 세계적으로 연구의 독창성을 인정받고 있다. 이것뿐만 아니라 2010년부터 HBM 상용화 설계에 직접 참여하고 있다. 그 결과, 현재의 인공지능 시대를 가능하게 했다는 평가를 받는다.

최근에는 6세대 HBM인 HBM4를 비롯해, HBM5, HBM6와 같은 차세대 HBM 구조와 아키텍트를 주도적으로 연구 중이다. 여기에 한 걸음 더 나아가 HBM 설계를 인공지능으로 자동화하려는 시도를 병행하고 있다. 특히 강화학습과 생성 인공지능을 결합해 HBM의 전기적, 열적 최적화 연구를 세계적 수준으로 이끌며, 이 분야의 연구를 선도하고 있다.

작년 6월에는, 삼성전자와 공동으로 KAIST에 ‘시스템아키텍트대학원’을 설립해 인공지능 반도체 분야 H/W 및 S/W 동시 설계가 가능한 고급 전문 인력을 양성하는 데 힘쓰고 있으며, 2018년부터 삼성전자 산학협력센터장을 맡고 있다. 또 네이버 ‧ 인텔과 협력해 KAIST에 AI 공동연구센터(NIK AI Research Center)를 설립하는 등 AI 반도체 설계와 더불어 AI 클라우드, AI 데이터 센터 성능 최적화를 목표로 반도체 산업의 신생태계 구축에도 기여하고 있다.

IEEE(국제전기전자공학자학회) 석학회원(Fellow)인 김 교수는 이와 같이 반도체 분야 연구와 교육을 통해 산업 발전에 기여한 공로를 인정받아 KAIST 학술상, KAIST 연구대상, KAIST 국제협력상, IEEE 기술 업적상 등을 수상했으며. IEEE 등 여러 국제학회에서 20여 차례에 걸쳐 '최고 논문상‘을 받는 등 학술적인 면에서도 큰 성과를 거두고 있다.

‘강대원 상’은 한국반도체학술대회 상임운영위원회가 세계적인 반도체 연구자인 고(故) 강대원 박사의 업적을 재조명하기 위해 지난 2017년, 처음 제정한 상이다. 강 박사는 미국 벨연구소에 입사해 1960년 이집트 출신 아탈라 박사와 트랜지스터 모스펫(MOS-FET)을 개발, 현대 반도체 기술의 핵심 토대를 마련했다. 또 플래시메모리 근간인 플로팅게이트를 세계 최초로 개발하기도 했다.

한편 한국반도체산업협회와 한국반도체연구조합, DB하이텍이 12~14일 강원도 하이원그랜드호텔에서 개최하는 32회 한국반도체학술대회에는 삼성전자·SK하이닉스·DB하이텍 등 반도체 기업을 포함해 국내 4,200명 이상의 반도체 분야 산·학·연 전문가와 학생이 참석해 역대 최대 규모인 1,659편 논문을 발표하는 등 연구 성과를 공유한다.

2025.02.12 조회수 2895

김정호 교수, 한국반도체학술대회 ‘2025 강대원 상’ 수상

우리 대학 전기및전자공학부 김정호 교수가 회로·시스템 분야 '2025년 강대원 상'을 한국반도체학술대회 상임운영위원회로부터 수상한다. 김 교수는 HBM 개발에 기여한 공로를 인정받아 SK하이닉스 이강욱 부사장과 함께 수상한다. 시상식은 13일 오후 강원도 하이원그랜드호텔에서 한국반도체산업협회 · 한국반도체연구조합 · DB하이텍이 공동으로 주관, 개최하는 ‘제32회 한국반도체학술대회(KCS 2025)’ 개막식에서 진행된다.

강대원 상은 세계 최초로 모스펫(MOSFET)과 플로팅게이트를 개발해, 반도체 기술 발전에 신기원을 이룩한 고(故) 강대원 박사를 기리기 위해 제정되었으며, 한국반도체학술대회 상임운영위원회가 지난 2017년 열린 제24회 반도체 학술대회부터 강대원 박사를 이을 인재들을 발굴, 선정해서 시상하고 있다.

김정호 교수는 ‘HBM 아버지’로 불리는 인공지능 반도체 분야의 세계적 권위자이다. 지난 20년 이상 HBM 관련 설계 기술을 세계적으로 주도해 왔다. 특히 HBM 실리콘관통전극(TSV), 인터포저, 신호선 설계(SI), 전력선 설계(PI) 등을 연구하며 세계적으로 연구의 독창성을 인정받고 있다. 이것뿐만 아니라 2010년부터 HBM 상용화 설계에 직접 참여하고 있다. 그 결과, 현재의 인공지능 시대를 가능하게 했다는 평가를 받는다.

최근에는 6세대 HBM인 HBM4를 비롯해, HBM5, HBM6와 같은 차세대 HBM 구조와 아키텍트를 주도적으로 연구 중이다. 여기에 한 걸음 더 나아가 HBM 설계를 인공지능으로 자동화하려는 시도를 병행하고 있다. 특히 강화학습과 생성 인공지능을 결합해 HBM의 전기적, 열적 최적화 연구를 세계적 수준으로 이끌며, 이 분야의 연구를 선도하고 있다.

작년 6월에는, 삼성전자와 공동으로 KAIST에 ‘시스템아키텍트대학원’을 설립해 인공지능 반도체 분야 H/W 및 S/W 동시 설계가 가능한 고급 전문 인력을 양성하는 데 힘쓰고 있으며, 2018년부터 삼성전자 산학협력센터장을 맡고 있다. 또 네이버 ‧ 인텔과 협력해 KAIST에 AI 공동연구센터(NIK AI Research Center)를 설립하는 등 AI 반도체 설계와 더불어 AI 클라우드, AI 데이터 센터 성능 최적화를 목표로 반도체 산업의 신생태계 구축에도 기여하고 있다.

IEEE(국제전기전자공학자학회) 석학회원(Fellow)인 김 교수는 이와 같이 반도체 분야 연구와 교육을 통해 산업 발전에 기여한 공로를 인정받아 KAIST 학술상, KAIST 연구대상, KAIST 국제협력상, IEEE 기술 업적상 등을 수상했으며. IEEE 등 여러 국제학회에서 20여 차례에 걸쳐 '최고 논문상‘을 받는 등 학술적인 면에서도 큰 성과를 거두고 있다.

‘강대원 상’은 한국반도체학술대회 상임운영위원회가 세계적인 반도체 연구자인 고(故) 강대원 박사의 업적을 재조명하기 위해 지난 2017년, 처음 제정한 상이다. 강 박사는 미국 벨연구소에 입사해 1960년 이집트 출신 아탈라 박사와 트랜지스터 모스펫(MOS-FET)을 개발, 현대 반도체 기술의 핵심 토대를 마련했다. 또 플래시메모리 근간인 플로팅게이트를 세계 최초로 개발하기도 했다.

한편 한국반도체산업협회와 한국반도체연구조합, DB하이텍이 12~14일 강원도 하이원그랜드호텔에서 개최하는 32회 한국반도체학술대회에는 삼성전자·SK하이닉스·DB하이텍 등 반도체 기업을 포함해 국내 4,200명 이상의 반도체 분야 산·학·연 전문가와 학생이 참석해 역대 최대 규모인 1,659편 논문을 발표하는 등 연구 성과를 공유한다.

2025.02.12 조회수 2895 -

스스로 학습·수정하는 뉴로모픽 반도체칩 개발

기존 컴퓨터 시스템은 데이터 처리 장치와 저장 장치가 분리돼 있어, 인공지능처럼 복잡한 데이터를 처리하기에는 효율적이지 않다. KAIST 연구팀은 우리 뇌의 정보 처리 방식과 유사한 멤리스터 기반 통합 시스템을 개발했다. 이제 원격 클라우드 서버에 의존하지 않고 의심스러운 활동을 즉시 인식하는 스마트 보안 카메라부터 건강 데이터를 실시간으로 분석할 수 있는 의료기기까지 다양한 분야에 적용될 수 있게 되었다.

우리 대학 전기및전자공학부 최신현 교수, 윤영규 교수 공동연구팀이 스스로 학습하고 오류를 수정할 수 있는 차세대 뉴로모픽 반도체 기반 초소형 컴퓨팅 칩을 개발했다고 17일 밝혔다.

연구팀이 개발한 이 컴퓨팅 칩의 특별한 점은 기존 뉴로모픽 소자에서 해결이 어려웠던 비이상적 특성에서 발생하는 오류를 스스로 학습하고 수정할 수 있다는 것이다. 예를 들어, 영상 스트림을 처리할 때 칩은 움직이는 물체를 배경에서 자동으로 분리하는 법을 학습하며 시간이 지날수록 이 작업을 더 잘 수행하게 된다.

이러한 자가 학습 능력은 실시간 영상 처리에서 이상적인 컴퓨터 시뮬레이션에 견줄 만한 정확도를 달성하며 입증됐다. 연구팀의 주요성과는 뇌와 유사한 구성 요소의 개발을 넘어, 신뢰성과 실용성을 모두 갖춘 시스템으로 완성한 것에 있다.

연구팀은 세계 최초로 즉각적인 환경 변화에 적응할 수 있는 멤리스터 기반 통합 시스템을 개발하며, 기존 기술의 한계를 극복하는 혁신적인 해결책을 제시했다.

이 혁신의 핵심에는 멤리스터(memristor)*라고 불리는 차세대 반도체 소자가 있다. 이 소자의 가변 저항 특성은 신경망의 시냅스 역할을 대체할 수 있게 되고, 이를 활용해 우리 뇌세포처럼 데이터 저장 및 연산을 동시에 수행할 수 있다.

*멤리스터: 메모리(memory)와 저항(resistor)의 합성어로 두 단자 사이로 과거에 흐른 전하량과 방향에 따라 저항값이 결정되는 차세대 전기소자

연구팀은 저항 변화를 정밀하게 제어할 수 있는 고신뢰성 멤리스터를 설계하고, 자가 학습을 통해 복잡한 보정 과정을 배제한 효율적인 시스템을 개발했다. 이번 연구는 실시간 학습과 추론을 지원하는 차세대 뉴로모픽 반도체 기반 통합 시스템의 상용화 가능성을 실험적으로 검증했다는 점에서 중요한 의미를 가진다.

이 기술은 일상적인 기기에서 인공지능을 사용하는 방식을 혁신하여 AI 작업 처리를 위해 원격 클라우드 서버에 의존하지 않고 로컬에서 처리할 수 있게 되어, 더 빠르고 사생활 보호가 강화되며 에너지 효율성이 높아질 것이다.

이 기술 개발을 주도한 KAIST 정학천 연구원과 한승재 연구원은 “이 시스템은 책상과 자료 캐비닛을 오가며 일하는 대신 모든 것이 손이 닿는 곳에 있는 스마트 작업 공간과 같다. 이는 모든 것이 한 곳에서 처리돼 매우 효율적인 우리 뇌의 정보 처리 방식과 유사하다”고 설명했다.

전기및전자공학부 정학천 석박통합과정생과 한승재 석박사통합과정생이 제 1저자로 연구에 참여했으며 국제 학술지 `네이처 일렉트로닉스 (Nature Electronics)'에 2025년 1월 8일 자로 온라인 게재됐다.

(논문 제목: Self-supervised video processing with self-calibration on an analogue computing platform based on a selector-less memristor array, https://doi.org/10.1038/s41928-024-01318-6)

이번 연구는 한국연구재단의 차세대지능형반도체기술개발사업, 우수신진연구사업, PIM인공지능반도체핵심기술개발사업, 정보통신기획평가원의 한국전자통신연구원연구개발지원사업의 지원을 받아 수행됐다.

2025.01.22 조회수 5123

스스로 학습·수정하는 뉴로모픽 반도체칩 개발

기존 컴퓨터 시스템은 데이터 처리 장치와 저장 장치가 분리돼 있어, 인공지능처럼 복잡한 데이터를 처리하기에는 효율적이지 않다. KAIST 연구팀은 우리 뇌의 정보 처리 방식과 유사한 멤리스터 기반 통합 시스템을 개발했다. 이제 원격 클라우드 서버에 의존하지 않고 의심스러운 활동을 즉시 인식하는 스마트 보안 카메라부터 건강 데이터를 실시간으로 분석할 수 있는 의료기기까지 다양한 분야에 적용될 수 있게 되었다.

우리 대학 전기및전자공학부 최신현 교수, 윤영규 교수 공동연구팀이 스스로 학습하고 오류를 수정할 수 있는 차세대 뉴로모픽 반도체 기반 초소형 컴퓨팅 칩을 개발했다고 17일 밝혔다.

연구팀이 개발한 이 컴퓨팅 칩의 특별한 점은 기존 뉴로모픽 소자에서 해결이 어려웠던 비이상적 특성에서 발생하는 오류를 스스로 학습하고 수정할 수 있다는 것이다. 예를 들어, 영상 스트림을 처리할 때 칩은 움직이는 물체를 배경에서 자동으로 분리하는 법을 학습하며 시간이 지날수록 이 작업을 더 잘 수행하게 된다.

이러한 자가 학습 능력은 실시간 영상 처리에서 이상적인 컴퓨터 시뮬레이션에 견줄 만한 정확도를 달성하며 입증됐다. 연구팀의 주요성과는 뇌와 유사한 구성 요소의 개발을 넘어, 신뢰성과 실용성을 모두 갖춘 시스템으로 완성한 것에 있다.

연구팀은 세계 최초로 즉각적인 환경 변화에 적응할 수 있는 멤리스터 기반 통합 시스템을 개발하며, 기존 기술의 한계를 극복하는 혁신적인 해결책을 제시했다.

이 혁신의 핵심에는 멤리스터(memristor)*라고 불리는 차세대 반도체 소자가 있다. 이 소자의 가변 저항 특성은 신경망의 시냅스 역할을 대체할 수 있게 되고, 이를 활용해 우리 뇌세포처럼 데이터 저장 및 연산을 동시에 수행할 수 있다.

*멤리스터: 메모리(memory)와 저항(resistor)의 합성어로 두 단자 사이로 과거에 흐른 전하량과 방향에 따라 저항값이 결정되는 차세대 전기소자

연구팀은 저항 변화를 정밀하게 제어할 수 있는 고신뢰성 멤리스터를 설계하고, 자가 학습을 통해 복잡한 보정 과정을 배제한 효율적인 시스템을 개발했다. 이번 연구는 실시간 학습과 추론을 지원하는 차세대 뉴로모픽 반도체 기반 통합 시스템의 상용화 가능성을 실험적으로 검증했다는 점에서 중요한 의미를 가진다.

이 기술은 일상적인 기기에서 인공지능을 사용하는 방식을 혁신하여 AI 작업 처리를 위해 원격 클라우드 서버에 의존하지 않고 로컬에서 처리할 수 있게 되어, 더 빠르고 사생활 보호가 강화되며 에너지 효율성이 높아질 것이다.

이 기술 개발을 주도한 KAIST 정학천 연구원과 한승재 연구원은 “이 시스템은 책상과 자료 캐비닛을 오가며 일하는 대신 모든 것이 손이 닿는 곳에 있는 스마트 작업 공간과 같다. 이는 모든 것이 한 곳에서 처리돼 매우 효율적인 우리 뇌의 정보 처리 방식과 유사하다”고 설명했다.

전기및전자공학부 정학천 석박통합과정생과 한승재 석박사통합과정생이 제 1저자로 연구에 참여했으며 국제 학술지 `네이처 일렉트로닉스 (Nature Electronics)'에 2025년 1월 8일 자로 온라인 게재됐다.

(논문 제목: Self-supervised video processing with self-calibration on an analogue computing platform based on a selector-less memristor array, https://doi.org/10.1038/s41928-024-01318-6)

이번 연구는 한국연구재단의 차세대지능형반도체기술개발사업, 우수신진연구사업, PIM인공지능반도체핵심기술개발사업, 정보통신기획평가원의 한국전자통신연구원연구개발지원사업의 지원을 받아 수행됐다.

2025.01.22 조회수 5123 -

강유전체 활용 차세대 반도체 메모리 혁신

강유전체는 메모리 소자에서 전하를 잘 저장하기 때문에 "전기를 기억하는 소재"와 같다는 특성으로 차세대 반도체 기술 개발에 있어 핵심 소재로 부각되고 있다. 우리 연구진이 이러한 강유전체 소재를 활용해 현재 메모리 반도체 산업의 양대 산맥인 디램(DRAM)과 낸드 플래시(NAND Flash) 메모리의 한계를 극복한 고성능, 고집적 차세대 메모리 소자를 개발하는데 성공했다.

우리 대학 전상훈 교수 연구팀이 하프니아 강유전체 소재*를 활용한 차세대 메모리 및 스토리지 메모리 기술을 개발했다고 6일 밝혔다.

*하프니아 강유전체 소재: 비휘발성 절연막으로, CMOS 공정 호환성, 동작 속도, 내구성 등의 우수한 물리적 특성을 바탕으로 차세대 반도체의 핵심 소재로 활발하게 연구되고 있는 물질

디램 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 휘발성 메모리다. 휘발성 특성으로 인해, 외부 전력이 끊어지면 저장된 데이터가 손실되지만, 공정 단가가 낮고 집적도가 높아 메인 메모리로 활용돼 왔다. 하지만 디램 메모리 기술은 소자의 크기가 작아질수록 디램 소자가 정보를 저장하는 저장 커패시터의 용량도 작아지게 되고, 더 이상 메모리 동작을 수행하기 어렵다.

연구팀은 저장 커패시터는 정보를 저장하는 디램 기술의 한계를 극복하고자 이러한 저장 커패시터가 물리적으로 작은 면적에서도 높은 저장 용량을 달성할 수 있도록 개선하는 데에 집중했다. 이를 위해 하프니아 강유전체 기반 극박막의 고유전율 물질을 개발했다. 연구 결과 현재까지 보고된 디램 커패시터 중, 가장 낮은 2.4 Å (머리카락 굵기의 약 10만분의 1)의 SiO2(실리콘 산화물) 유효 두께와 같이 얇은 층에 저장하는 것을 달성했다.

또한 연구팀은 디램 메모리 기술을 잠재적으로 대체할 수 있는 후보군으로 주목받고 있는 강유전체 메모리 FRAM 메모리도 개발하였다. 현 DRAM 수준의 1V 이하의 낮은 전압에서도 비 휘발성 정보 저장과 삭제가 확실히 이루어지는 기술은 에너지 효율성을 크게 향상시켜 차세대 메모리에 필수적이다.

디램 메모리 기술에 이어 연구팀은 낸드 플래시 메모리의 한계를 극복할 하프니아 강유전체 기반의 차세대 메모리 기술을 개발했다. 낸드 플래시 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 비휘발성 메모리이다. 현재, 낸드플래시 메모리의 저장 용량을 늘리기 위해 여러 층을 쌓아 올리는 방식으로 발전해 왔지만, 물리적인 한계로 인해 500층, 1000층 이상으로 쌓기가 어려운 상황이다.

이에 연구팀은 강유전체라는 새로운 소재를 낸드 플래시에 적용하는 방식을 연구한 결과, 소재 계면에 TiO2 층이라는 얇은 층을 추가함으로써 1000단 이상의 수직 적층 3차원이며 외부 환경의 간섭에도 데이터를 안정적으로 유지하도록 설계했다.

마지막으로 기존의 낸드 플래시 기술에서 산화물 채널 기반의 메모리 소자는 데이터를 완전히 지울 수 없는 한계가 있어 새로운 구조의 고성능 산화물 채널 기반 낸드 플래시 소자를 개발하는 데 성공했다. 이 소자는 더 많은 데이터를 저장할 수 있고 데이터를 10년 이상 안정적으로 보존할 수 있는 특징을 가진다.

전상훈 교수는 “이번 연구 결과들은 스케일링 이슈로 인해 답보상태에 있는 메모리 반도체 기술 개발에 돌파구가 되는 기술이 될 것으로 판단되며, 향후 다양한 인공지능 컴퓨팅 및 엣지 컴퓨팅 기술 상용화에 기여할 수 있을 것”이라고 설명했다.

벤카테스왈루 가담(Venkateswarlu Gaddam) 연구 교수, 김기욱 박사 과정, 조홍래 박사 과정, 황정현 박사 과정, 이상호 박사 과정, 최효준 석사 과정, 강현준 석사 과정이 공동 제1 저자로 참여했고 이러한 연구 성과를 국제적으로 인정받아 반도체 산업계 최고 수준의(Top-tier) 컨퍼런스에 2024년 5편의 논문을 발표했다. (2024 VLSI 2편, 2024 IEDM 3편)

- In-depth analysis of the Hafnia ferroelectrics as a key enabler for low voltage & QLC 3D VNAND beyond 1K layers: Experimental demonstration and modeling VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Low-Damage Processed and High-Pressure Annealed High-k Hafnium Zirconium Oxide Capacitors near Morphotropic Phase Boundary with Record-Low EOT of 2.4 Å & high-k of 70 for DRAM … VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Unveiling the Origin of Disturbance in FeFET and the Potential of Multifunctional TiO2 as a Breakthrough for Disturb-free 3D NAND Cell: Experimental and Modeling https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=4

- Oxide Channel Ferroelectric NAND Device with Source- tied Covering Metal Structure: Wide Memory Window (14.3 V), Reliable Retention (> 10 years) and Disturbance Immunity (△Vth ≤ 0.1 V) for QLC Operation

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=47

- Design Methodology for Low-Voltage Operational (≤1 V) FRAM Cell Capacitors and Approaches for Overcoming Disturb Issues in 1T-nC Arrays: Experimental & Modeling:

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=54

참고로, IEEE VLSI와 IEEE IEDM 학회는 삼성전자, SK 하이닉스, 마이크론, 인텔 등 굴지의 반도체 업계와 세계적인 석학들이 최신 기술 개발을 공유하고 미래 기술의 지향점을 논의하는 학회로 반도체 올림픽이라고 불린다.

한편, 이 연구는 삼성전자, 한양대학교와 협업을 통해서 수행되었으며, 한국산업기술평가원 (KEIT) 민관공동투자 반도체 고급인력양성사업, 과학기술정보통신부 혁신연구센터(IRC) 지원 사업, 삼성전자(Samsung Electronics)의 지원을 받아 진행됐다.

2025.01.06 조회수 5975

강유전체 활용 차세대 반도체 메모리 혁신

강유전체는 메모리 소자에서 전하를 잘 저장하기 때문에 "전기를 기억하는 소재"와 같다는 특성으로 차세대 반도체 기술 개발에 있어 핵심 소재로 부각되고 있다. 우리 연구진이 이러한 강유전체 소재를 활용해 현재 메모리 반도체 산업의 양대 산맥인 디램(DRAM)과 낸드 플래시(NAND Flash) 메모리의 한계를 극복한 고성능, 고집적 차세대 메모리 소자를 개발하는데 성공했다.

우리 대학 전상훈 교수 연구팀이 하프니아 강유전체 소재*를 활용한 차세대 메모리 및 스토리지 메모리 기술을 개발했다고 6일 밝혔다.

*하프니아 강유전체 소재: 비휘발성 절연막으로, CMOS 공정 호환성, 동작 속도, 내구성 등의 우수한 물리적 특성을 바탕으로 차세대 반도체의 핵심 소재로 활발하게 연구되고 있는 물질

디램 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 휘발성 메모리다. 휘발성 특성으로 인해, 외부 전력이 끊어지면 저장된 데이터가 손실되지만, 공정 단가가 낮고 집적도가 높아 메인 메모리로 활용돼 왔다. 하지만 디램 메모리 기술은 소자의 크기가 작아질수록 디램 소자가 정보를 저장하는 저장 커패시터의 용량도 작아지게 되고, 더 이상 메모리 동작을 수행하기 어렵다.

연구팀은 저장 커패시터는 정보를 저장하는 디램 기술의 한계를 극복하고자 이러한 저장 커패시터가 물리적으로 작은 면적에서도 높은 저장 용량을 달성할 수 있도록 개선하는 데에 집중했다. 이를 위해 하프니아 강유전체 기반 극박막의 고유전율 물질을 개발했다. 연구 결과 현재까지 보고된 디램 커패시터 중, 가장 낮은 2.4 Å (머리카락 굵기의 약 10만분의 1)의 SiO2(실리콘 산화물) 유효 두께와 같이 얇은 층에 저장하는 것을 달성했다.

또한 연구팀은 디램 메모리 기술을 잠재적으로 대체할 수 있는 후보군으로 주목받고 있는 강유전체 메모리 FRAM 메모리도 개발하였다. 현 DRAM 수준의 1V 이하의 낮은 전압에서도 비 휘발성 정보 저장과 삭제가 확실히 이루어지는 기술은 에너지 효율성을 크게 향상시켜 차세대 메모리에 필수적이다.

디램 메모리 기술에 이어 연구팀은 낸드 플래시 메모리의 한계를 극복할 하프니아 강유전체 기반의 차세대 메모리 기술을 개발했다. 낸드 플래시 메모리는 우리가 스마트폰, 컴퓨터, USB 등에서 사용하는 데이터를 저장하는 비휘발성 메모리이다. 현재, 낸드플래시 메모리의 저장 용량을 늘리기 위해 여러 층을 쌓아 올리는 방식으로 발전해 왔지만, 물리적인 한계로 인해 500층, 1000층 이상으로 쌓기가 어려운 상황이다.

이에 연구팀은 강유전체라는 새로운 소재를 낸드 플래시에 적용하는 방식을 연구한 결과, 소재 계면에 TiO2 층이라는 얇은 층을 추가함으로써 1000단 이상의 수직 적층 3차원이며 외부 환경의 간섭에도 데이터를 안정적으로 유지하도록 설계했다.

마지막으로 기존의 낸드 플래시 기술에서 산화물 채널 기반의 메모리 소자는 데이터를 완전히 지울 수 없는 한계가 있어 새로운 구조의 고성능 산화물 채널 기반 낸드 플래시 소자를 개발하는 데 성공했다. 이 소자는 더 많은 데이터를 저장할 수 있고 데이터를 10년 이상 안정적으로 보존할 수 있는 특징을 가진다.

전상훈 교수는 “이번 연구 결과들은 스케일링 이슈로 인해 답보상태에 있는 메모리 반도체 기술 개발에 돌파구가 되는 기술이 될 것으로 판단되며, 향후 다양한 인공지능 컴퓨팅 및 엣지 컴퓨팅 기술 상용화에 기여할 수 있을 것”이라고 설명했다.

벤카테스왈루 가담(Venkateswarlu Gaddam) 연구 교수, 김기욱 박사 과정, 조홍래 박사 과정, 황정현 박사 과정, 이상호 박사 과정, 최효준 석사 과정, 강현준 석사 과정이 공동 제1 저자로 참여했고 이러한 연구 성과를 국제적으로 인정받아 반도체 산업계 최고 수준의(Top-tier) 컨퍼런스에 2024년 5편의 논문을 발표했다. (2024 VLSI 2편, 2024 IEDM 3편)

- In-depth analysis of the Hafnia ferroelectrics as a key enabler for low voltage & QLC 3D VNAND beyond 1K layers: Experimental demonstration and modeling VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Low-Damage Processed and High-Pressure Annealed High-k Hafnium Zirconium Oxide Capacitors near Morphotropic Phase Boundary with Record-Low EOT of 2.4 Å & high-k of 70 for DRAM … VLSI 24 DOI: 10.1109/VLSITechnologyandCir46783.2024

- Unveiling the Origin of Disturbance in FeFET and the Potential of Multifunctional TiO2 as a Breakthrough for Disturb-free 3D NAND Cell: Experimental and Modeling https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=4

- Oxide Channel Ferroelectric NAND Device with Source- tied Covering Metal Structure: Wide Memory Window (14.3 V), Reliable Retention (> 10 years) and Disturbance Immunity (△Vth ≤ 0.1 V) for QLC Operation

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=47

- Design Methodology for Low-Voltage Operational (≤1 V) FRAM Cell Capacitors and Approaches for Overcoming Disturb Issues in 1T-nC Arrays: Experimental & Modeling:

https://iedm24.mapyourshow.com/8_0/sessions/session-details.cfm?scheduleid=54

참고로, IEEE VLSI와 IEEE IEDM 학회는 삼성전자, SK 하이닉스, 마이크론, 인텔 등 굴지의 반도체 업계와 세계적인 석학들이 최신 기술 개발을 공유하고 미래 기술의 지향점을 논의하는 학회로 반도체 올림픽이라고 불린다.

한편, 이 연구는 삼성전자, 한양대학교와 협업을 통해서 수행되었으며, 한국산업기술평가원 (KEIT) 민관공동투자 반도체 고급인력양성사업, 과학기술정보통신부 혁신연구센터(IRC) 지원 사업, 삼성전자(Samsung Electronics)의 지원을 받아 진행됐다.

2025.01.06 조회수 5975 -

실리콘 한계 넘는 양극성 반도체 소자 개발

차세대 2차원 층상구조 나노소재로 주목받는 인듐 셀레나이드(InSe)는 실리콘 반도체보다 전자 이동도가 뛰어나고 포화 속도가 두 배 이상 빠른 장점을 가지지만, 주로 N형 반도체로만 사용되어 왔다. 우리 연구진이 이를 극복하고 N형 및 P형, 양극에 우수한 성능을 제공하는 인듐 셀레나이드 기반 기술을 개발하여 차세대 전자 소자의 설계 및 상용화 가능성을 크게 앞당길 것으로 기대된다.

우리 대학 전기및전자공학부 이가영 교수 연구팀이 나노 반도체 인듐 셀레나이드(InSe)* 기반 혁신적인 양극성 다기능 트랜지스터를 개발했다고 30일 밝혔다.

*인듐 셀레나이드(InSe): 인듐과 셀레늄으로 이루어진 무기 화합물 반도체로 2차원 층간 결합을 이루고 있음

인듐 셀레나이드는 N형 반도체로만 사용되어 왔는데, 이는 P형 반도체 및 상보적 회로 구현에 필요한 양(P) 전하를 띄는 정공*을 유도하기 어렵다는 문제 때문으로 이는 상용화의 큰 걸림돌로 작용해 왔다.

*정공: P형 트랜지스터 구현에 필요한 양 전하를 띠는 입자

이가영 교수 연구팀은 정공 유도를 위해 추가적인 공정이나 다른 물질을 접목하는 다양한 시도에도 해결되지 못했던 문제점을 새로운 소자 구조 설계를 통해 해결했다. 이번에 공개된 양극성 반도체 소자는 N형과 P형 트랜지스터에 모두 적용이 가능하다.

연구팀은 인듐 셀레나이드 하부에 전극을 배치하고 금속-반도체 접합 특성을 개선함으로써, 전자와 정공이 선택적으로 흐를 수 있는 양극성 특성을 구현하는 데 성공했다.

특히, 이번 연구에서는 N형 및 P형 전류 꺼짐/켜짐 비가 모두 109(10억) 이상에 달하는 우수한 성능을 기록했다. 실리콘 반도체 소자의 경우 일반적으로 108 이하 꺼짐/켜짐 비의 단극성 구동을 띄며, N형과 P형 구동이 동시에 가능한 양극성 2차원 반도체*의 경우도 N형과 P형 꺼짐/켜짐 비가 동시에 108 이상인 경우는 없었다.

*2차원 반도체: 2차원 방향으로만 강한 원자 결합을 이루며 수직 방향으로는 층상구조를 가져 층상구조 반도체라고 불리기도 함

이가영 교수는 “다기능 소자들은 일반적으로 복잡한 공정 과정과 구조를 요구해 제작과 집적에 어려움이 있다. 그러나 이번 연구에서는 간단한 부분 게이트 구조를 도입해 하나의 소자에서 다양한 기능을 구현할 수 있는 다기능 소자를 제작하는 데 성공했다”며 “이 기술은 공정 효율성을 높이고 회로 설계 유연성 향상에 기여할 것으로 기대된다”고 설명했다.

또한 “이번 연구는 인듐 셀레나이드를 기반으로 한 P형 응용 가능성을 새롭게 밝혔으며, 궁극적으로는 상보적 다기능 시스템으로서의 활용 가능성을 보여준다”고 덧붙였다.

전기및전자공학부 김민수 석박통합과정, 염동주 석사과정, 석용욱 박사과정 학생이 공동 제1 저자로 참여한 이번 연구는 나노 물리 분야 저명 국제 학술지 ‘나노 레터스(Nano Letters)’에 2024년 12월 18일 출판됐으며 동시에 저널 표지 논문으로 채택됐다. (논문명: Superior P-Type Switching in InSe Nanosheets for Complementary Multifunctional Systems, https://doi.org/10.1021/acs.nanolett.4c04624)

한편 이번 연구는 한국기초과학지원연구원 국가연구시설장비진흥센터, 한국연구재단 우수연구사업, KAIST 도약연구(UP) 사업, 그리고 삼성전자의 지원을 받아 수행됐다.

2024.12.30 조회수 5001

실리콘 한계 넘는 양극성 반도체 소자 개발

차세대 2차원 층상구조 나노소재로 주목받는 인듐 셀레나이드(InSe)는 실리콘 반도체보다 전자 이동도가 뛰어나고 포화 속도가 두 배 이상 빠른 장점을 가지지만, 주로 N형 반도체로만 사용되어 왔다. 우리 연구진이 이를 극복하고 N형 및 P형, 양극에 우수한 성능을 제공하는 인듐 셀레나이드 기반 기술을 개발하여 차세대 전자 소자의 설계 및 상용화 가능성을 크게 앞당길 것으로 기대된다.

우리 대학 전기및전자공학부 이가영 교수 연구팀이 나노 반도체 인듐 셀레나이드(InSe)* 기반 혁신적인 양극성 다기능 트랜지스터를 개발했다고 30일 밝혔다.

*인듐 셀레나이드(InSe): 인듐과 셀레늄으로 이루어진 무기 화합물 반도체로 2차원 층간 결합을 이루고 있음

인듐 셀레나이드는 N형 반도체로만 사용되어 왔는데, 이는 P형 반도체 및 상보적 회로 구현에 필요한 양(P) 전하를 띄는 정공*을 유도하기 어렵다는 문제 때문으로 이는 상용화의 큰 걸림돌로 작용해 왔다.

*정공: P형 트랜지스터 구현에 필요한 양 전하를 띠는 입자

이가영 교수 연구팀은 정공 유도를 위해 추가적인 공정이나 다른 물질을 접목하는 다양한 시도에도 해결되지 못했던 문제점을 새로운 소자 구조 설계를 통해 해결했다. 이번에 공개된 양극성 반도체 소자는 N형과 P형 트랜지스터에 모두 적용이 가능하다.

연구팀은 인듐 셀레나이드 하부에 전극을 배치하고 금속-반도체 접합 특성을 개선함으로써, 전자와 정공이 선택적으로 흐를 수 있는 양극성 특성을 구현하는 데 성공했다.

특히, 이번 연구에서는 N형 및 P형 전류 꺼짐/켜짐 비가 모두 109(10억) 이상에 달하는 우수한 성능을 기록했다. 실리콘 반도체 소자의 경우 일반적으로 108 이하 꺼짐/켜짐 비의 단극성 구동을 띄며, N형과 P형 구동이 동시에 가능한 양극성 2차원 반도체*의 경우도 N형과 P형 꺼짐/켜짐 비가 동시에 108 이상인 경우는 없었다.

*2차원 반도체: 2차원 방향으로만 강한 원자 결합을 이루며 수직 방향으로는 층상구조를 가져 층상구조 반도체라고 불리기도 함

이가영 교수는 “다기능 소자들은 일반적으로 복잡한 공정 과정과 구조를 요구해 제작과 집적에 어려움이 있다. 그러나 이번 연구에서는 간단한 부분 게이트 구조를 도입해 하나의 소자에서 다양한 기능을 구현할 수 있는 다기능 소자를 제작하는 데 성공했다”며 “이 기술은 공정 효율성을 높이고 회로 설계 유연성 향상에 기여할 것으로 기대된다”고 설명했다.

또한 “이번 연구는 인듐 셀레나이드를 기반으로 한 P형 응용 가능성을 새롭게 밝혔으며, 궁극적으로는 상보적 다기능 시스템으로서의 활용 가능성을 보여준다”고 덧붙였다.

전기및전자공학부 김민수 석박통합과정, 염동주 석사과정, 석용욱 박사과정 학생이 공동 제1 저자로 참여한 이번 연구는 나노 물리 분야 저명 국제 학술지 ‘나노 레터스(Nano Letters)’에 2024년 12월 18일 출판됐으며 동시에 저널 표지 논문으로 채택됐다. (논문명: Superior P-Type Switching in InSe Nanosheets for Complementary Multifunctional Systems, https://doi.org/10.1021/acs.nanolett.4c04624)

한편 이번 연구는 한국기초과학지원연구원 국가연구시설장비진흥센터, 한국연구재단 우수연구사업, KAIST 도약연구(UP) 사업, 그리고 삼성전자의 지원을 받아 수행됐다.

2024.12.30 조회수 5001 -

전기및전자공학부 김태수 석사과정, IEEE EDAPS 2024 국제학회 최우수논문상 수상

아시아·태평양지역에서 가장 권위 있는 반도체 패키징 기술 관련 국제학회 ‘EDAPS(Electrical Design of Advanced Packaging & Systems) 2024’에서 전기및전자공학부 김정호 교수 연구실 석사과정 김태수 학생이 ‘최우수 논문상’을 수상했다고 26일 밝혔다.

‘이뎁스(EDAPS)’는 아시아·태평양 지역에서 가장 큰 규모와 영향력을 지닌 반도체 패키징 기술 관련 학회로, 지난 2002년부터 국제전기전자공학자협회(IEEE) Electronic Packaging Society가 매년 주최하고 있다.

주로 전기 공학 분야에서 활동하는 학계 연구자와 산업계 엔지니어가 참석하며, 칩(Chip) 설계, 시스템인 패키지·시스템 온 패키지(Sip/Sop), 전자파 간섭·전자 적합성(EMI/EMC), 설계 자동화 프로그램(EDA) 툴(Tool) 및 3D-IC 및 실리콘 관통 전극(TSV) 설계 등 반도체 패키징의 전반적인 분야에 대해, 연구 결과를 공유하고 산업계의 요구사항을 반영한 연구를 진행할 수 있는 기회를 제공하는 것으로 유명하다.

EDAPS 학회는 매년 열리는 학회 마지막 날, 해당 연도에 제출된 논문 중 최우수 논문상, 최우수 학생 논문상과 최우수 포스터 상 등 3개 부문의 수상 논문을 뽑아 발표한다.

“김태수 석사과정 학생은 지난 12월 17일부터 사흘간 인도 벵갈루루에서 열린 ‘EDAPS 2024’ 국제학회에서 ‘Twin Tower HBM’이란 주제의 논문으로 2024년에 출판된 40여 편의 논문 중 해당 분야의 기술혁신에 기여한 점을 인정받아 ‘EDAPS 2024 전체 최우수 논문상(Best Paper Award)’을 수상했다”고 관계자는 설명했다.

김태수 학생이 ‘Twin Tower HBM’이라는 주제로 최우수 논문상을 수상한 이 논문은 마치 쌍둥이 빌딩처럼 두 개의 DRAM 스택을 단일 베이스 다이(Base Die)에 통합해 메모리 용량을 기존 대비 2배로 확대하는 한편 대역폭을 27.9% 향상시켰으며, 신호 무결성 검증을 위해 채널 설계 최적화와 3D EM 시뮬레이션을 병행한 내용으로 큰 주목을 받았다.

특히 김태수 학생은 생성형 AI의 초거대 모델을 효과적으로 지원하기 위해 기존 메모리 용량과 대역폭의 한계를 수평적으로(Horizontally) 확장하는 방식으로 극복한 독창적인 연구를 수행했다는 점에서 심사위원들로부터 높은 평가를 받은 것으로 알려졌다.

김태수 학생은 “이번 연구의 주제와 내용을 정리하는데 ‘HBM의 아버지’로 불리는 김정호 교수님의 지도와 함께 올 6월부터 4개월간 미국 실리콘밸리에 위치한 삼성전자 미주법인(DSA)에서의 인턴 생활 경험이 많은 도움이 됐다”면서, 앞으로 HBM 중심 컴퓨팅(HCC: HBM Centric Computing)을 수립하는 데 도움을 줄 수 있을 것”이라고 기대했다.

그는 이어 “AGI(인공 일반 지능, Artificial General Intelligence) 실현을 위해 SiP(시스템인 패키지) 기반의 칩렛(Chiplet) 구조와 하드웨어-소프트웨어 협업 설계를 더욱 심화하여 차세대 인공지능 플랫폼의 토대를 마련하겠다”고 포부를 밝혔다.

한편, 김정호 교수 연구실(TERA Lab)에는 올 12월 말 현재 석사과정 12명, 박사과정 14명 등 모두 26명의 학생이 반도체 전·후공정에 들어가는 다양한 패키지와 인터커넥션 설계를 강화·모방 학습과 같은 인공지능(AI) 머신러닝(ML)을 활용해 최적화하는 연구를 수행 중이다.

김정호 교수 연구실은 이번 김태수 석사과정 학생의 수상 외에도 지난 2021년 신태인 박사과정 학생이 ‘EDAPS 2021 전체 최우수 논문상’을 수상한 바 있다.

이밖에 같은 해(2021년)에 반도체 설계 분야에서 세계적으로 권위를 인정받고 있는 국제학술대회‘디자인콘(DesignCon)’에서도 김민수 석사과정 학생이‘최우수 논문상’을, 그리고 2023년 말에는 전체 수상자 총 8명 중 김성국·최성욱·신태인·김혜연 박사과정 학생 등 4명이 동시에 최우수 논문상을 받아 큰 화제를 모은 바 있다.

2024.12.26 조회수 4471

전기및전자공학부 김태수 석사과정, IEEE EDAPS 2024 국제학회 최우수논문상 수상

아시아·태평양지역에서 가장 권위 있는 반도체 패키징 기술 관련 국제학회 ‘EDAPS(Electrical Design of Advanced Packaging & Systems) 2024’에서 전기및전자공학부 김정호 교수 연구실 석사과정 김태수 학생이 ‘최우수 논문상’을 수상했다고 26일 밝혔다.

‘이뎁스(EDAPS)’는 아시아·태평양 지역에서 가장 큰 규모와 영향력을 지닌 반도체 패키징 기술 관련 학회로, 지난 2002년부터 국제전기전자공학자협회(IEEE) Electronic Packaging Society가 매년 주최하고 있다.

주로 전기 공학 분야에서 활동하는 학계 연구자와 산업계 엔지니어가 참석하며, 칩(Chip) 설계, 시스템인 패키지·시스템 온 패키지(Sip/Sop), 전자파 간섭·전자 적합성(EMI/EMC), 설계 자동화 프로그램(EDA) 툴(Tool) 및 3D-IC 및 실리콘 관통 전극(TSV) 설계 등 반도체 패키징의 전반적인 분야에 대해, 연구 결과를 공유하고 산업계의 요구사항을 반영한 연구를 진행할 수 있는 기회를 제공하는 것으로 유명하다.

EDAPS 학회는 매년 열리는 학회 마지막 날, 해당 연도에 제출된 논문 중 최우수 논문상, 최우수 학생 논문상과 최우수 포스터 상 등 3개 부문의 수상 논문을 뽑아 발표한다.

“김태수 석사과정 학생은 지난 12월 17일부터 사흘간 인도 벵갈루루에서 열린 ‘EDAPS 2024’ 국제학회에서 ‘Twin Tower HBM’이란 주제의 논문으로 2024년에 출판된 40여 편의 논문 중 해당 분야의 기술혁신에 기여한 점을 인정받아 ‘EDAPS 2024 전체 최우수 논문상(Best Paper Award)’을 수상했다”고 관계자는 설명했다.

김태수 학생이 ‘Twin Tower HBM’이라는 주제로 최우수 논문상을 수상한 이 논문은 마치 쌍둥이 빌딩처럼 두 개의 DRAM 스택을 단일 베이스 다이(Base Die)에 통합해 메모리 용량을 기존 대비 2배로 확대하는 한편 대역폭을 27.9% 향상시켰으며, 신호 무결성 검증을 위해 채널 설계 최적화와 3D EM 시뮬레이션을 병행한 내용으로 큰 주목을 받았다.

특히 김태수 학생은 생성형 AI의 초거대 모델을 효과적으로 지원하기 위해 기존 메모리 용량과 대역폭의 한계를 수평적으로(Horizontally) 확장하는 방식으로 극복한 독창적인 연구를 수행했다는 점에서 심사위원들로부터 높은 평가를 받은 것으로 알려졌다.

김태수 학생은 “이번 연구의 주제와 내용을 정리하는데 ‘HBM의 아버지’로 불리는 김정호 교수님의 지도와 함께 올 6월부터 4개월간 미국 실리콘밸리에 위치한 삼성전자 미주법인(DSA)에서의 인턴 생활 경험이 많은 도움이 됐다”면서, 앞으로 HBM 중심 컴퓨팅(HCC: HBM Centric Computing)을 수립하는 데 도움을 줄 수 있을 것”이라고 기대했다.

그는 이어 “AGI(인공 일반 지능, Artificial General Intelligence) 실현을 위해 SiP(시스템인 패키지) 기반의 칩렛(Chiplet) 구조와 하드웨어-소프트웨어 협업 설계를 더욱 심화하여 차세대 인공지능 플랫폼의 토대를 마련하겠다”고 포부를 밝혔다.

한편, 김정호 교수 연구실(TERA Lab)에는 올 12월 말 현재 석사과정 12명, 박사과정 14명 등 모두 26명의 학생이 반도체 전·후공정에 들어가는 다양한 패키지와 인터커넥션 설계를 강화·모방 학습과 같은 인공지능(AI) 머신러닝(ML)을 활용해 최적화하는 연구를 수행 중이다.

김정호 교수 연구실은 이번 김태수 석사과정 학생의 수상 외에도 지난 2021년 신태인 박사과정 학생이 ‘EDAPS 2021 전체 최우수 논문상’을 수상한 바 있다.

이밖에 같은 해(2021년)에 반도체 설계 분야에서 세계적으로 권위를 인정받고 있는 국제학술대회‘디자인콘(DesignCon)’에서도 김민수 석사과정 학생이‘최우수 논문상’을, 그리고 2023년 말에는 전체 수상자 총 8명 중 김성국·최성욱·신태인·김혜연 박사과정 학생 등 4명이 동시에 최우수 논문상을 받아 큰 화제를 모은 바 있다.

2024.12.26 조회수 4471 -

美케이던스社, 80억 상당 AI반도체 장비 우리 대학에 기증

“케이던스 사의 통 큰 기부에 감사드리며, 대한민국 AI 인재 100만 명 양성이라는 원대한 목표 달성과 세상을 혁신할 반도체 연구 실현에 앞장서겠습니다”(이광형 총장)

우리 대학은 미국 소프트웨어 기업인 케이던스 디자인 시스템즈 코리아(Cadence Design Systems, 이하 케이던스)가 반도체 설계 특화 장비인 ‘케이던스 팔라디움 제트원(Cadence Palladium Z1)’*을 우리 대학에 기증한다고 밝혔다.

*팔라디움 제트원: 반도체 설계 검증을 위한 초고성능 에뮬레이터 장비로, 하드웨어-소프트웨어 검증 및 디버깅 작업을 1개의 랙 당 5.76억 게이트까지 대용량으로 구현 가능함. 동 장비를 통해 SoC(System On Chip) 개발 단계에서 설계 검증을 더 원활히 수행할 수 있음.

케이던스는 1995년 반도체설계교육센터(IDEC) 설립 이후 우리 대학에 EDA(Electronic Design Automation) 툴 라이센스 및 실습 교육을 약 30년간 지원해왔다. 이 인연을 계기로 반도체 설계 인력 양성에 도움이 되고자 하는 뜻을 담아 기증이 성사됐다.

17일(화) 오전 열리는 기증식에는 이광형 총장, 유회준 인공지능반도체대학원장, 박인철 반도체설계교육센터 소장, 케이던스 신용석 사장, 케이던스 도지훈 상무 등 교내외 관계자들이 참석한다.

기증식에서 박인철 반도체설계교육센터 소장과 조우영 PIM반도체설계연구센터 교수가 기증 경과와 운영 계획을 발표하고, 우리 대학과 케이던스가 업무협약을 체결할 예정이다.

이후 반도체설계교육센터(IDEC)는 팔라디움 제트원 사용법 교육을 신설하고 국내 대학 연구실에서 본 장비를 활용할 수 있도록 시스템·기술 기반을 마련한다.

PIM 반도체설계연구센터와 인공지능반도체대학원은 산학협력 연구기관 및 스타트업을 중심으로 장비 사용 환경을 구축한다. 케이던스는 실제 운용을 위한 관리자 교육과 필요한 소프트웨어 등을 지원하기로 하였다.

신용석 케이던스 코리아 사장은 “이번 기증과 우리 대학과의 협력을 통해 반도체 산업을 이끌어갈 우수 인재가 더 많아지길 바란다. 앞으로도 케이던스는 선진 반도체 기술 구현을 위해 최선을 다할 것”이라고 밝혔다.

이광형 총장은“케이던스코리아의 우수 장비 기증에 감사드리며, 이를 통해 반도체 역량 성장의 중요한 발판이 마련된 것을 기쁘게 생각한다. 우리 대학은 반도체 분야 선도기관으로서, 새로운 교육 기회와 혁신적인 연구를 통해 대한민국 반도체 산업의 글로벌 경쟁력 강화에 기여할 것”이라고 전했다.

케이던스는 1983년에 설립된 미국의 다국적 기술 및 컴퓨팅 소프트웨어 기업으로 집적회로, 시스템 온 칩(SoC), 인쇄 회로 기판 및 다중물리 시스템 분석(MSA) 등의 제품 설계를 위한 소프트웨어 및 하드웨어를 제작하는 곳이다. 현재 삼성전자 파운드리 사업부의 EDA 공식 파트너로서 국내 반도체 기업의 칩 설계를 위한 소프트웨어와 하드웨어를 공급하고 있다.

2024.12.17 조회수 4482

美케이던스社, 80억 상당 AI반도체 장비 우리 대학에 기증

“케이던스 사의 통 큰 기부에 감사드리며, 대한민국 AI 인재 100만 명 양성이라는 원대한 목표 달성과 세상을 혁신할 반도체 연구 실현에 앞장서겠습니다”(이광형 총장)

우리 대학은 미국 소프트웨어 기업인 케이던스 디자인 시스템즈 코리아(Cadence Design Systems, 이하 케이던스)가 반도체 설계 특화 장비인 ‘케이던스 팔라디움 제트원(Cadence Palladium Z1)’*을 우리 대학에 기증한다고 밝혔다.

*팔라디움 제트원: 반도체 설계 검증을 위한 초고성능 에뮬레이터 장비로, 하드웨어-소프트웨어 검증 및 디버깅 작업을 1개의 랙 당 5.76억 게이트까지 대용량으로 구현 가능함. 동 장비를 통해 SoC(System On Chip) 개발 단계에서 설계 검증을 더 원활히 수행할 수 있음.

케이던스는 1995년 반도체설계교육센터(IDEC) 설립 이후 우리 대학에 EDA(Electronic Design Automation) 툴 라이센스 및 실습 교육을 약 30년간 지원해왔다. 이 인연을 계기로 반도체 설계 인력 양성에 도움이 되고자 하는 뜻을 담아 기증이 성사됐다.

17일(화) 오전 열리는 기증식에는 이광형 총장, 유회준 인공지능반도체대학원장, 박인철 반도체설계교육센터 소장, 케이던스 신용석 사장, 케이던스 도지훈 상무 등 교내외 관계자들이 참석한다.

기증식에서 박인철 반도체설계교육센터 소장과 조우영 PIM반도체설계연구센터 교수가 기증 경과와 운영 계획을 발표하고, 우리 대학과 케이던스가 업무협약을 체결할 예정이다.

이후 반도체설계교육센터(IDEC)는 팔라디움 제트원 사용법 교육을 신설하고 국내 대학 연구실에서 본 장비를 활용할 수 있도록 시스템·기술 기반을 마련한다.

PIM 반도체설계연구센터와 인공지능반도체대학원은 산학협력 연구기관 및 스타트업을 중심으로 장비 사용 환경을 구축한다. 케이던스는 실제 운용을 위한 관리자 교육과 필요한 소프트웨어 등을 지원하기로 하였다.

신용석 케이던스 코리아 사장은 “이번 기증과 우리 대학과의 협력을 통해 반도체 산업을 이끌어갈 우수 인재가 더 많아지길 바란다. 앞으로도 케이던스는 선진 반도체 기술 구현을 위해 최선을 다할 것”이라고 밝혔다.

이광형 총장은“케이던스코리아의 우수 장비 기증에 감사드리며, 이를 통해 반도체 역량 성장의 중요한 발판이 마련된 것을 기쁘게 생각한다. 우리 대학은 반도체 분야 선도기관으로서, 새로운 교육 기회와 혁신적인 연구를 통해 대한민국 반도체 산업의 글로벌 경쟁력 강화에 기여할 것”이라고 전했다.

케이던스는 1983년에 설립된 미국의 다국적 기술 및 컴퓨팅 소프트웨어 기업으로 집적회로, 시스템 온 칩(SoC), 인쇄 회로 기판 및 다중물리 시스템 분석(MSA) 등의 제품 설계를 위한 소프트웨어 및 하드웨어를 제작하는 곳이다. 현재 삼성전자 파운드리 사업부의 EDA 공식 파트너로서 국내 반도체 기업의 칩 설계를 위한 소프트웨어와 하드웨어를 공급하고 있다.

2024.12.17 조회수 4482 -

반도체 정밀 공정 흐린 영상 복원 가능하다

생물학 연구에 사용되는 형광 현미경이나 반도체 산업에 사용되는 주사전자현미경의 공통점은 불안정성으로 인해 흐려진 영상(블러, blur)을 보정하는 과정이 반드시 필요하다는 점이다. 우리 연구진이 굉장히 강한 잡음에 의해 손상된 왜곡 영상에 대해 적응형 필터와 생성형 인공지능 모델을 융합해 영상을 복원하는 데 성공했다.

우리 대학 바이오및뇌공학과 장무석 교수 연구팀이 삼성전자 DS부문 반도체연구소 차세대공정개발실과 공동 연구를 통해 왜곡 및 강한 잡음이 존재하는 의료·산업 영상을 복원하는 기술을 개발했다고 26일 밝혔다.

스마트폰 카메라 사진에 영상의 흐림·왜곡이 생겼을 때 보정하는 문제를 디컨볼루션(deconvolution) 또는 디블러링(deblurring)이라고 하며, 흐려진 영상 정보만 이용해 선명한 영상을 복원하는 기술을 블라인드 디컨볼루션(blind deconvolution)이라고 한다. 흥미롭게도 디컨볼루션 문제는 일상뿐만 아니라 생물학 연구, 반도체 산업 등 다양한 분야에서 공통적으로 발생한다.

예를 들어, 형광 현미경은 세포와 분자 수준의 미세 구조를 시각화하기 때문에 측정된 형광 신호는 산란이나 회절, 수차 등의 효과로 인해 흐려지기 때문에 디컨볼루션 기법을 통해 보정하는 과정이 반드시 필요하다.

또한, 반도체 산업에서는 수천 개의 생산 공정 중간에 검사·계측 기술을 통해 발생할 수 있는 미세 공정 오류를 감지하고, 공정 수율 개선을 위한 프로세스 개선 과정에 사용되는 주사전자현미경이 전자 빔의 불안정성으로 인해 영상이 흐려지기 쉬우며, 이를 보정하는 과정이 반드시 필요하다.

연구팀은 이처럼 영상이 흐려지는 원인은 움직임, 빛의 산란, 전자의 불안정성 등과 같이 다양하지만, 공통적으로 ‘영상의 흐려짐을 없앤다’라는 점에서 수학적으로 동일한 접근 방법이 활용될 수 있다고 생각했다.

특히 잡음 수준이 높은 영상의 경우, 영상의 잡음을 효과적으로 억제함과 동시에 블러 효과가 제거된 선명한 영상을 복원하는 과정의 균형을 맞추는 것이 매우 중요하다는 점을 착안했다.

연구팀은 위너 디컨볼루션*을 기반으로 영상을 복원하는 접근법을 개발했다. 이를 적응형 잡음 억제 변수, 영상 생성형 인공지능 모델과 결합해 영상 복원 과정에서 발생할 수 있는 잡음을 억제하고 영상 선명도도 높였다.

*위너 디컨볼루션(Wiener deconvolution)은 왜곡된 영상을 역 필터(inverse filter)를 기반으로 깨끗한 영상으로 복원하는 전통적인 방식임.

연구팀은 잡음 민감도가 높은 주사전자현미경으로부터 측정된 왜곡된 영상으로부터 깨끗하고 초점이 맞는 나노미터 단위의 반도체 구조에 대한 영상을 성공적으로 복원해 냄으로써 반도체 검사·계측에 매우 효과적으로 적용할 수 있음을 실험적으로 증명했다.

바이오및뇌공학과 이찬석 연구원은 “이번 연구를 통해 강한 잡음 속에서 왜곡된 영상을 복원하는 난제를 해결했다ˮ며, 이어 "이번 연구에서는 무작위적 잡음을 극복하는 영상 복원 기술을 개발하는 데에 집중했고, 향후 비균일 영상 복원 및 다양한 손상 형태를 극복하는 영상 복원 기술 개발에 주력할 것이다ˮ라고 밝혔다.

바이오및뇌공학과 이찬석 박사과정이 제1 저자로 참여한 이번 연구는 컴퓨터 비전 분야 최고 학회인 ‘제18회 유럽 컴퓨터 비전 학회(The 18th European Conference on Computer Vision)’ 에서 지난 10월 1일에 이탈리아 밀란에서 발표됐고, Springer Nature에서 출판하는 Lecture Notes in Computer Science의 ECCV 2024 프로시딩 집에 게재될 예정이다. (논문명: Blind image deblurring with noise-robust kernel estimation).

2024.11.26 조회수 4421

반도체 정밀 공정 흐린 영상 복원 가능하다

생물학 연구에 사용되는 형광 현미경이나 반도체 산업에 사용되는 주사전자현미경의 공통점은 불안정성으로 인해 흐려진 영상(블러, blur)을 보정하는 과정이 반드시 필요하다는 점이다. 우리 연구진이 굉장히 강한 잡음에 의해 손상된 왜곡 영상에 대해 적응형 필터와 생성형 인공지능 모델을 융합해 영상을 복원하는 데 성공했다.

우리 대학 바이오및뇌공학과 장무석 교수 연구팀이 삼성전자 DS부문 반도체연구소 차세대공정개발실과 공동 연구를 통해 왜곡 및 강한 잡음이 존재하는 의료·산업 영상을 복원하는 기술을 개발했다고 26일 밝혔다.

스마트폰 카메라 사진에 영상의 흐림·왜곡이 생겼을 때 보정하는 문제를 디컨볼루션(deconvolution) 또는 디블러링(deblurring)이라고 하며, 흐려진 영상 정보만 이용해 선명한 영상을 복원하는 기술을 블라인드 디컨볼루션(blind deconvolution)이라고 한다. 흥미롭게도 디컨볼루션 문제는 일상뿐만 아니라 생물학 연구, 반도체 산업 등 다양한 분야에서 공통적으로 발생한다.

예를 들어, 형광 현미경은 세포와 분자 수준의 미세 구조를 시각화하기 때문에 측정된 형광 신호는 산란이나 회절, 수차 등의 효과로 인해 흐려지기 때문에 디컨볼루션 기법을 통해 보정하는 과정이 반드시 필요하다.

또한, 반도체 산업에서는 수천 개의 생산 공정 중간에 검사·계측 기술을 통해 발생할 수 있는 미세 공정 오류를 감지하고, 공정 수율 개선을 위한 프로세스 개선 과정에 사용되는 주사전자현미경이 전자 빔의 불안정성으로 인해 영상이 흐려지기 쉬우며, 이를 보정하는 과정이 반드시 필요하다.

연구팀은 이처럼 영상이 흐려지는 원인은 움직임, 빛의 산란, 전자의 불안정성 등과 같이 다양하지만, 공통적으로 ‘영상의 흐려짐을 없앤다’라는 점에서 수학적으로 동일한 접근 방법이 활용될 수 있다고 생각했다.

특히 잡음 수준이 높은 영상의 경우, 영상의 잡음을 효과적으로 억제함과 동시에 블러 효과가 제거된 선명한 영상을 복원하는 과정의 균형을 맞추는 것이 매우 중요하다는 점을 착안했다.

연구팀은 위너 디컨볼루션*을 기반으로 영상을 복원하는 접근법을 개발했다. 이를 적응형 잡음 억제 변수, 영상 생성형 인공지능 모델과 결합해 영상 복원 과정에서 발생할 수 있는 잡음을 억제하고 영상 선명도도 높였다.

*위너 디컨볼루션(Wiener deconvolution)은 왜곡된 영상을 역 필터(inverse filter)를 기반으로 깨끗한 영상으로 복원하는 전통적인 방식임.

연구팀은 잡음 민감도가 높은 주사전자현미경으로부터 측정된 왜곡된 영상으로부터 깨끗하고 초점이 맞는 나노미터 단위의 반도체 구조에 대한 영상을 성공적으로 복원해 냄으로써 반도체 검사·계측에 매우 효과적으로 적용할 수 있음을 실험적으로 증명했다.

바이오및뇌공학과 이찬석 연구원은 “이번 연구를 통해 강한 잡음 속에서 왜곡된 영상을 복원하는 난제를 해결했다ˮ며, 이어 "이번 연구에서는 무작위적 잡음을 극복하는 영상 복원 기술을 개발하는 데에 집중했고, 향후 비균일 영상 복원 및 다양한 손상 형태를 극복하는 영상 복원 기술 개발에 주력할 것이다ˮ라고 밝혔다.

바이오및뇌공학과 이찬석 박사과정이 제1 저자로 참여한 이번 연구는 컴퓨터 비전 분야 최고 학회인 ‘제18회 유럽 컴퓨터 비전 학회(The 18th European Conference on Computer Vision)’ 에서 지난 10월 1일에 이탈리아 밀란에서 발표됐고, Springer Nature에서 출판하는 Lecture Notes in Computer Science의 ECCV 2024 프로시딩 집에 게재될 예정이다. (논문명: Blind image deblurring with noise-robust kernel estimation).

2024.11.26 조회수 4421